# D3.3 "FINAL RELEASE OF THE TASK-BASED RUNTIME"

#### **Version 1.0**

#### **Document Information**

| Contract Number      | 780681                                                                                                                                                                                                                                                                   |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Project Website      | https://legato-project.eu/                                                                                                                                                                                                                                               |  |

| Contractual Deadline | 31 May 2020                                                                                                                                                                                                                                                              |  |

| Dissemination Level  | Public                                                                                                                                                                                                                                                                   |  |

| Nature               | Report                                                                                                                                                                                                                                                                   |  |

| Author               | Miquel Pericàs (CHALMERS)                                                                                                                                                                                                                                                |  |

| Contributors         | Do Le Quoc (TUD), Xavier Martorell (BSC), Leonardo<br>Bautista-Gomez (BSC), Behzad Salami (BSC), Mustafa<br>Abduljabbar (CHALMERS), Gunnar Billung-Meyer<br>(CHR), Omar Shaaban Ibrahim (BSC), Jimmy Aguilar<br>Mena (BSC), Paul Carpenter (BSC), Tobias Becker<br>(MAX) |  |

| Reviewers            | Micha vor dem Berge (CHR)                                                                                                                                                                                                                                                |  |

The LEGaTO project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement No 780681.

Version 1.0 1 / 73

# **Change Log**

| Version | Description of Change                                                                         |

|---------|-----------------------------------------------------------------------------------------------|

| 1239    | 2020-04-01, File created                                                                      |

| 1245    | 2020-04-12, Deliverable outline                                                               |

| 1276    | 2020-04-28, Middleware                                                                        |

| 1280    | 2020-05-03, FPGA Undervolting                                                                 |

| 1292    | 2020-05-04, XiTAO energy-aware scheduler, topologies, pipeline parallelism and extrae support |

| 1306    | 2020-05-08, Trusted Key Management                                                            |

| 1312    | 2020-05-11, FPGA Checkpointing                                                                |

| 1313    | 2020-05-11, OmpSs@Cluster                                                                     |

| 1317    | 2020-05-12, GPU Checkpointing                                                                 |

| 1324    | 2020-05-13, OmpS@FPGA, OmpSs@linter, backend drivers                                          |

| 1332    | 2020-05-18, Conclusion                                                                        |

| 1343    | 2020-05-21, CHR reviews applied                                                               |

| 1364    | 2020-05-28, SLiC API                                                                          |

| 1367    | 2020-05-31, Release Candidate RC1                                                             |

This log reflects actual revision numbers from SVN (version control software used).

Version 1.0 2 / 73

# Index

| Exec                                          | cutive Summary                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intro                                         | oduction                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Mide<br>3.1<br>3.2<br>3.3<br>3.4              | Redfish API                                                      | 11<br>13<br>17<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Ene</b> i 4.1                              | XiTAO                                                            | 18<br>18<br>20<br>25<br>28<br>28<br>33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | GPU Checkpointing                                                | 43<br>43<br>44<br>44<br>45<br>45<br>47<br>48<br>49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.4                                           | 5.4.1 Approach: A Trusted Management Service                     | 50<br>51<br>55<br>57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Run</b> 6.1                                | OmpSs@Linter as a debug tool                                     | 58<br>59<br>63<br>65<br>68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                               | Intro Midd 3.1 3.2 3.3 3.4  Ener 4.1  4.2  Run 5.1  5.4  Run 6.1 | Middleware and backend drivers  3.1 Redfish API  3.2 Web GUI  3.3 RECS Platform Drivers  3.4 SLiC API  Energy-efficient task-based runtime  4.1 XiTAO  4.1.1 XiTAO software topologies  4.1.2 The XiTAO heterogeneous scheduler  4.1.3 Support for Pipeline Parallelism  4.2 OmpSs  4.2.1 OmpSs@FPGA  4.2.2 OmpSs@Cluster  Runtime support for Fault Tolerance and Security  5.1 GPU Checkpointing  5.1.1 Code Release  5.1.2 Paper Publication  5.2 FPGA Checkpointing  5.3 FPGA Unvervolting for CNN Accelerators  5.3.1 Introduction  5.3.2 Experimental Results: Voltage Behavior Analysis  5.3.3 Power-reliability Trade-off for Reduced-voltage FPGA-based CNN Accelerators  5.3.4 Frequency Underscaling  5.4 Trusted Key Management  5.4.1 Approach: A Trusted Management Service  5.4.2 Evaluation: Micro-benchmarks  5.4.3 Evaluation: Macro-benchmarks  6.1 OmpSs@Linter as a debug tool  6.1 OmpSs@Linter as a debug tool  6.1.1 OmpSs Linter  6.1.2 Evaluation: Results  6.1.3 Evaluation: Results |

| 7 | Conclusion | 68 |

|---|------------|----|

| 8 | References | 69 |

Version 1.0

# **List of Figures**

| 1.1                                                                         | The LEGaTO stack and relation of components with LEGaTO goals.                                                                                                                                                                                                               | 9                                            |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11 | Redfish API output of chassis fan monitoring data Redfish API output of baseboard power and current monitoring data RECS Box server Web GUI showing the management overview Node Composition Wizard - General preferences view Node Composition Wizard - Node selection view | 12<br>13<br>14<br>14<br>15<br>15<br>16<br>16 |

| 4.1<br>4.2<br>4.3                                                           | Virtual topology mapping of Jacobi2D and Copy2D kernels Adding an extra layer for NUMA-aware data placement                                                                                                                                                                  | 19<br>20<br>20                               |

| 4.4<br>4.5                                                                  | Energy efficient task scheduler runtime overview                                                                                                                                                                                                                             | 21                                           |

| 4.6                                                                         | two clusters in MAX and MIN frequencies                                                                                                                                                                                                                                      | 22                                           |

|                                                                             | and so on                                                                                                                                                                                                                                                                    | 25                                           |

| 4.7<br>4.8                                                                  | Step-by-step depiction of parallel pipeline stages in XiTAO runtime Execution time of 15 input units with different resource widths                                                                                                                                          | 26                                           |

|                                                                             | given to each pipeline stage                                                                                                                                                                                                                                                 | 28                                           |

| 4.9                                                                         | OmpSs@FPGA Matrix Multiply benchmark                                                                                                                                                                                                                                         | 30                                           |

| 4.10                                                                        | OmpSs compilation env. with FPGA support                                                                                                                                                                                                                                     | 30                                           |

| 4.11                                                                        | High-level representation of the Nanos++ environment                                                                                                                                                                                                                         | 31                                           |

| 4.12                                                                        | Evaluation of matrix multiplication on OmpSs@FPGA                                                                                                                                                                                                                            | 33                                           |

| 4.13                                                                        | Example of an OmpSs task with input dependencies over A and B                                                                                                                                                                                                                |                                              |

| 4.14                                                                        | arrays, and output dependency over C array                                                                                                                                                                                                                                   | 35                                           |

|                                                                             | space                                                                                                                                                                                                                                                                        | 36                                           |

| 4.15                                                                        | Nanos 6 task offloading model                                                                                                                                                                                                                                                | 37                                           |

Version 1.0 5 / 73

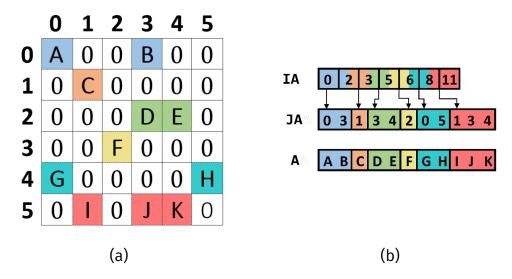

| 4.16       | Compressed Sparse Row (CSR) sparse matrix format representation. In (a) a 2D dense matrix, and (b) is the CSR representation of                                                                                    |          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.17       | (a)                                                                                                                                                                                                                | 39       |

| 4.18       | plication (SpMV) Routine                                                                                                                                                                                           | 40       |

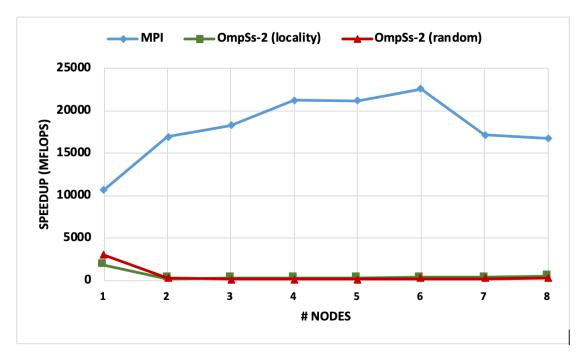

| 4.19       | tiplication (SpMV) of the scalar SpMV code from Figure 4.17 CSR-SpMV MPI vs. OmpSs-2 strong scalability of 24k x 24k sparse                                                                                        | 41       |

| 4.20       | matrix on MareNostrum 4                                                                                                                                                                                            | 41       |

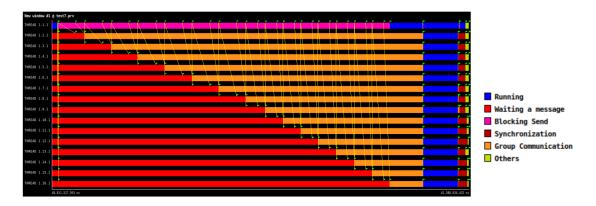

| 4.21       | flow of concurrent threads shown by the horizontal blue lines CSR SpMV OmpSs-2 execution trace of 24k x 24k sparse matrix on two nodes. (a) showing trace with no communication lines. (b) with communication line | 42       |

| 4.22       | Example of an OmpSs task that must execute on node 1                                                                                                                                                               | 42<br>43 |

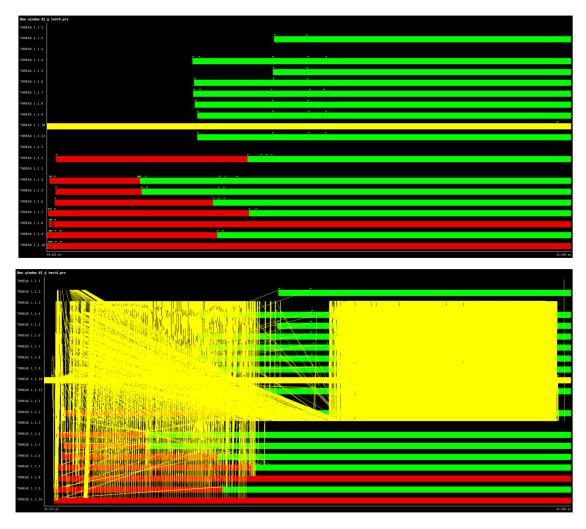

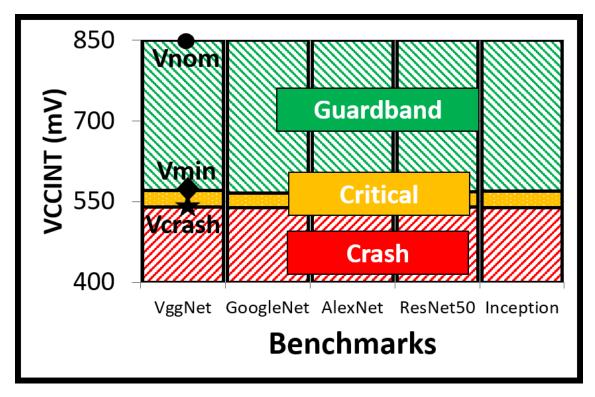

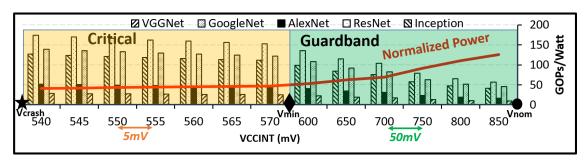

| 5.1        | Voltage regions with a slight workload-to-workload variation (averaged across three hardware platforms)                                                                                                            | 48       |

| 5.3<br>5.2 | Effect of reduced supply voltage on the accuracy of CNN workloads (separately for three hardware platforms)                                                                                                        | 49       |

| 5.2        | INT8 quantized and without pruning at ambient temperature (averaged across three hardware platforms)                                                                                                               | 49       |

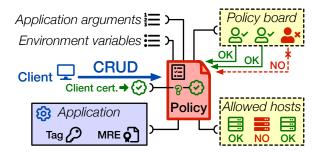

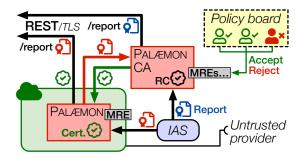

| 5.4        | Overview of security policies                                                                                                                                                                                      | 52       |

| 5.5        | Principle of managed PALAEMON deployment and operation                                                                                                                                                             | 52       |

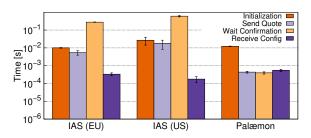

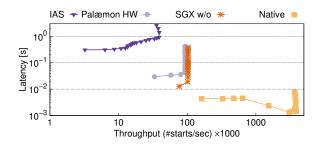

| 5.6        | Attestation and configuration latencies: even when located close to Intel's IAS server, attestation with IAS takes about an order of                                                                               | J-       |

|            | magnitude longer than with PALAEMON                                                                                                                                                                                | 56       |

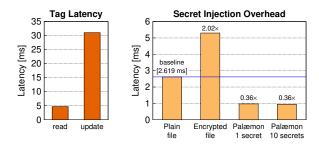

| 5.7<br>5.8 | Startup latency and throughput using attestation variants Left: latency of PALAEMON tag reads and updates. Right: reading overhead for a file with 1 or 10 secrets normalized by the time to                       | 56       |

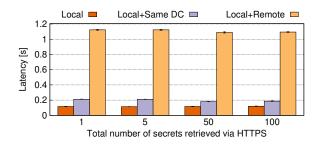

| 5.9        | read a plain file                                                                                                                                                                                                  | 57       |

|            | service deployed locally, from the same data centre (DC) or from an instance running on a different continent                                                                                                      | 57       |

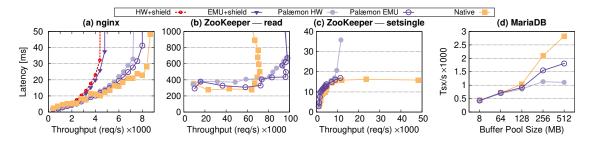

| 5.10       | (a) Throughput/latency for GET requests on 67kB files, in five variants of nginx. ZooKeeper: read (b) and write (c) operations. (d) MariaDB with TPC-C benchmark (d): increasing buffer pool helps                 | -0       |

|            | native more than EMU or hardware                                                                                                                                                                                   | 58       |

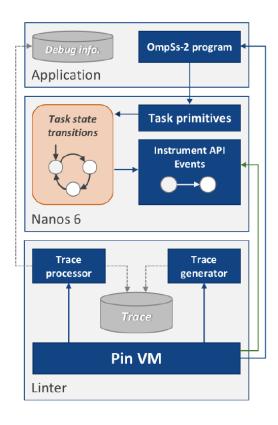

| 6.1        | OmpSs@Linter environment                                                                                                                                                                                           | 60       |

| 6.2        | Examples of use of the lint directive                                                                                                                                                                              | 62       |

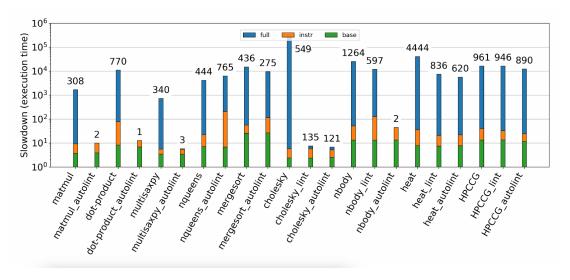

| 6.3<br>6.4 | Example of use of the verified clause                                                                                                                                                                              | 63       |

| _          | the benchmarks executed under OmpSs@Linter                                                                                                                                                                         | 67       |

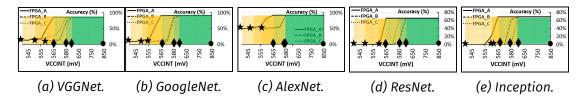

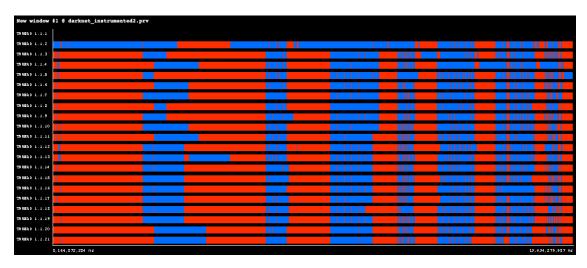

| 6.5        | VGG traces for two events.                                                                                                                                                                                         | 68       |

Version 1.0 6 / 73

# **List of Tables**

|     | Power consumption profile of compute-bound tasks Summary of evaluated schedulers                                                                                    | _  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1 | Evaluation of frequency underscaling to prevent CNN accuracy loss in the critical voltage region, at ambient temperature (averaged across three hardware platforms) | 50 |

Version 1.0 7 / 73

# 1. Executive Summary

This report describes the final release of the LEGaTO toolchain backend. It corresponds to the backend state as reached at M30. The report is organized in four sections covering:

- 1. The middleware and drivers to run on the LEGaTO hardware.

- 2. The energy-efficient runtime, with a focus on the two main components OmpSs/Nanos and XiTAO.

- 3. The runtime support for fault tolerance and security, focusing on fault tolerance for GPU/FPGA (via checkpointing), FPGA (undervolting reliability), and CPU security (trusted key management).

- 4. The runtime tools that have been introduced to support the development of applications written using with the LEGaTO toolchain.

This deliverable D3.3 extends and supersedes deliverable D3.2 "First release of the task-based runtime". To avoid overlap between the two documents, we choose to highlight only those components that are novel or have been considerably updated since D3.2. Overall, this deliverable covers work that has been done during the past 10 months, from M20 until M30. Throughout the deliverable, we attempt to highlight how this "final release" deliverable differs from D3.2 (the "first release").

This final runtime release includes many highlights. Dynamic node composition is now supported via the Redfish API and web GUI of the RECS|Box management software. At the runtime layer, the release includes a more advanced implementation of the XiTAO runtime, featuring (1) performance, interference and energy-aware scheduling, (2) virtual topologies for locality-aware scheduling, and (3) novel support for pipeline parallelism. The release also features advanced support for executing OmpSs applications on cluster hardware (OmpSs@Cluster), and improvements to OmpSs@FPGA targeting novel FPGA hardware, such as support for scalar operands, and instrumentation for performance analysis. To support program development, the OmpSs@Linter tool has been considerably extended, and the XiTAO runtime is now integrated with the Extrae/Paraver toolchain from BSC. Finally, this final release also features support for advanced fault tolerance in the form of high performance GPU/FPGA checkpointing, support for reliable and energy efficient FPGA undervolting, and trusted key management.

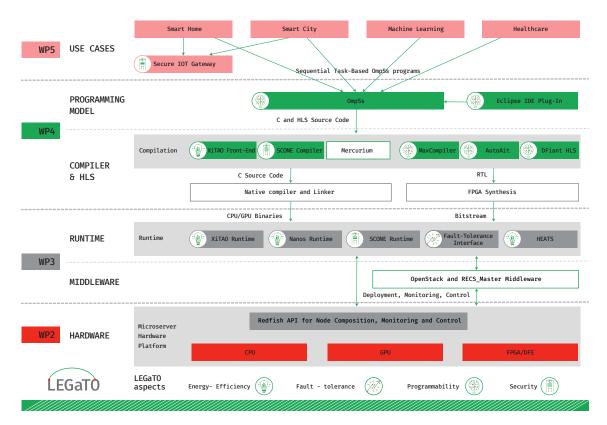

The various components of the LEGaTO backend and how they related to the major four goals of LEGaTO (energy efficiency, fault tolerance, security, and programmability) are shown in Figure 1.1.

Several components developed in the LEGaTO work package 3 "Tool-Chain Back-End" tasks (mainly in T3.4 "Energy-efficient Task-based Runtime") are tightly coupled with the toolchain front-end developed in work package 4. The description of the runtime components developed by Maxeler (MaxJ), Technion (DFiant) and University of Neuchatel (HEATS) is deferred to Deliverable D4.3 ("Final release

LEGaTO D3.3

Version 1.0 8 / 73

Figure 1.1. The LEGaTO stack and relation of components with LEGaTO goals

of energy-efficient, secure, resilient task-based programming model and compiler extensions, including FPGA toolchain"). D4.3 describes these components together with the rest of the front-end toolchain infrastructure.

### 2. Introduction

Optimizing application execution to utilize heterogeneous systems composed of asymmetric cores, FPGAs and GPUs is instrumental to reach the levels of energy efficiency demanded by next generation IoT, Edge and HPC applications. Over the past 2.5 years, the LEGaTO project has been building a toolchain to map applications written in the OmpSs language onto two heterogeneous platforms provided by Christmann and Maxeler. This deliverable (D3.3) describes the final LEGaTO release of the runtime system that has been developed to support LEGaTO applications via intelligent execution-time mechanisms. The main goal of the runtime stack developed is energy efficiency, with additional goals being productivity, fault tolerance and security.

This deliverable extends and supersedes Deliverable D3.2 which was submitted at M20. The focus of the deliverable is on novel and/or heavily updated components since D3.2. The application development and compilation aspects of the LEGaTO toolchain are covered in the sibling deliverable D4.3.

In order to achieve the targeted improvement of 10× energy reduction, LEGaTO's runtime work package (WP3) has been researching scheduling and locality-awareness techniques, the offloading of computations to FPGAs, and the undervolting of FPGAs. The main goal of the runtime is to make efficient use of the underlying

Version 1.0 9 / 73

hardware. This requires a good understanding of the available hardware and its configuration. The RECS hardware developed by Christmann and UBI can be statically configured, and dynamically queried and and configured by the runtime via the Redfish API and an optional OpenStack layer. The Redfish API is described in Section 3.1, along with the Web GUI designed to configure the RECS hardware which is described in 3.2. The work to target the RECS platform from the runtime layer is described in Section 3.3. On the other hand, the specific components to target the Maxeler DFE platform are described in Section 3.4.

In modern platforms, performance and energy-efficiency are highly dependent on data movement. To this end, we are developing novel APIs to specify application-level task locality in a platform-independent way. The XiTAO runtime supports a mechanism called software topologies which allows to map tasks on a virtual topology which is translated to the hardware topology at runtime. The operation of this scheme is described in Section 4.1.1 with a focus on virtual places mapping, a novel feature introduced in this release.

Several scheduling techniques have been researched in the context of the experimental XiTAO runtime. XiTAO decouples task parallelism from the amount of resources by specifying a resource container. Runtime-guided allocation of resource containers is a major target of our research, enabling the user to target performance-aware or energy-aware schedules. Our research on how to exploit moldability and task criticality to achieve reduced energy consumption is described in Section 4.1.2. We also describe a novel implementation of pipeline parallelism within XiTAO in Section 4.1.3.

FPGAs are becoming popular in HPC and in the datacenter as a way to accelerate applications with high energy efficiency. In LEGaTO, we have researched how to support FPGAs at runtime via the OmpSs@FPGA infrastructure which enables seamless offloading of FPGA bitstreams to FPGA accelerators, all integrated within the OmpSs compilation flow and Nanos runtime. Our research on OmpSs@FPGA is described in Section 4.2.1.

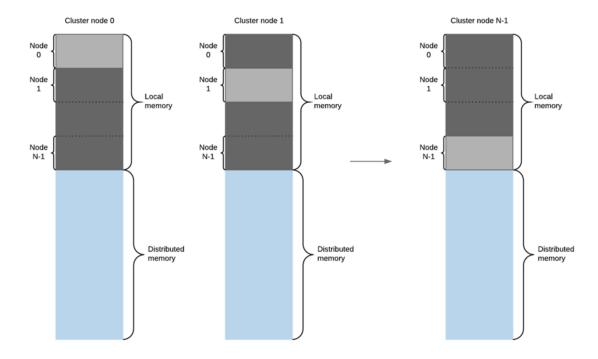

Scalability is another major goal of LEGaTO in order to support larger applications and systems. To achieve improved scalability, we have researched how to execute OmpSs applications on multiple nodes with distributed memory. This approach, called OmpSs@Cluster, has been released as part of OmpSs-2<sup>1</sup>. The technologies required to execute OmpSs applications on large-scale clusters are described in Section 4.2.2.

One challenge associated with scalability is reliability. Executing an application on a large collection of nodes decreases its Mean Time Before Failure (MTBF). Checkpointing is a common technique to increase reliability by storing application snapshots to long term storage (e.g. disk). Previously, checkpointing has been extensively researched in the context of CPUs. The LEGaTO project has researched how to extend this support to heterogeneous architectures including FPGA and GPU. Section 5.1 details our work on automatically checkpointing applications running on GPUs using the FTI checkpointing library. This D3.3 deliverable also includes a description of the novel FPGA checkpointing support in Section 5.2

https://pm.bsc.es/ompss-2

Version 1.0 10 / 73

Further energy-efficiency with FPGAs can be achieved by using undervolting. This technique reduces the voltage of FPGA components to achieve a more energy-efficient operation mode. However, too aggressive undervolting can lead to errors. How much to undervolt and how to correct errors are two goals that have been researched in LEGaTO. The results of this research are described in Section 5.3, with a focus on accelerators for convolutional neural networks (CNN).

Ensuring integrity and privacy is also an important goal of LEGaTO. Via LEGaTO's PALAEMON framwork it is now possible to transfer secrets in a trusted manner to applications running inside of enclaves such as Intel SGX. This work is described in Section 5.4.

Finally, we are also developing runtime components to support the programming of LEGaTO applications. The main focus is the tool OmpSs@Linter whose goal is to detect potential bugs in the specification of OmpSs task dependencies and missing synchronization between OmpSs parent and child tasks. This development is described in Section 6.1. This deliverable concludes with a description of novel performance debugging support integrated in XiTAO via the extrae/paraver toolchain 6.2.

### 3. Middleware and backend drivers

The hardware utilized in the LEGaTO project is of a very special kind. It features the usage of heterogeneous computing resources such as x86, ARM, GPUs, FPGAs and FPGA-based Dataflow Engines (DFEs) and allows to compose those resources statically and dynamically. This characteristic, called node composition, is made possible by the flexible high-speed low-latency communication infrastructure. It can be configured to connect resources with each other and can also be reconfigured during runtime to adapt to specific characteristics of computing algorithms. In addition to that, the hardware allows the dynamic distribution of PCIe functions among the connected resources. Further details and examples of node composition can be found in D2.2 [7].

The middleware layer of the LEGaTO software stack is developed within this project to handle those complex characteristics of the underlying hardware. It enables the upper software layers to interact with it and make use of its flexibility to enhance the efficiency of computation algorithms.

As already stated in chapter 3 of D3.2 [36], the focus of the middleware has been shifted from OpenStack development to the extension of the firmware, Redfish API and Web GUI embedded in the RECS|Box server itself. Those software parts were enhanced to take over the management tasks of OpenStack to allow easy and full-featured (re-)configuration of the underlying hardware, without OpenStack. Anyhow, the static part of the node composition process is still supported with OpenStack. This part was already described in section 3.2 in D3.2 [36].

#### 3.1. Redfish API

The hardware inventory of the RECS|Box can be accessed through the Redfish API, which was described in D3.2 [36]. Its documentation can be accessed online at Github [12]. This RESTful API is implemented in the embedded RECS\_Master

Version 1.0 11 / 73

management software of the RECS|Box. The API makes the capabilities of the underlying hardware visible and one can navigate through it to gather all required information about the hardware model like e.g. microservers and PCIe extension cards.

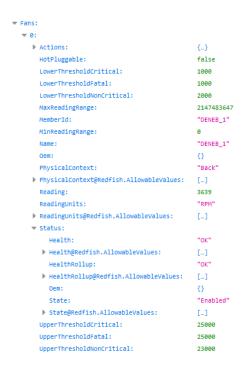

Because it is an essential feature to have a picture of the overall system health status, the API was enhanced within the LEGaTO project to now also contain detailed monitoring data regarding the thermal and power state of the hardware components. The figures 3.1 and 3.2 in this section show parts of the JSON output after querying the Redfish API.

Figure 3.1. Redfish API output of chassis fan monitoring data

Figure 3.2. Redfish API output of baseboard power and current monitoring data

Furthermore, the RECS\_Master management software was enhanced to expose more detailed information about PCIe functions through the Redfish API. This includes technical information such as bus, domain and instance numbers as well as vendor and device identifiers. Those identifiers, commonly known as VID

and DID, are then resolved to their names within the RECS\_Master to administer additional human readable information to the user.

#### 3.2. Web GUI

The RECS\_Master management software provides not only the Redfish API but also a comprehensive Web GUI to manage the hardware. As part of the RECS|Box server management system, it was developed in previous EU-funded projects and completely reworked and enhanced within the LEGaTO project.

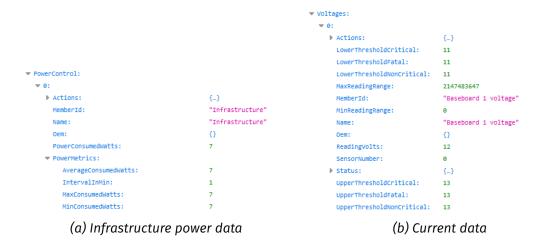

Figure 3.3. RECS|Box server Web GUI showing the management overview

Figure 3.3 shows a screenshot of the management overview of a RECS|Box server to get a picture of its capabilities.

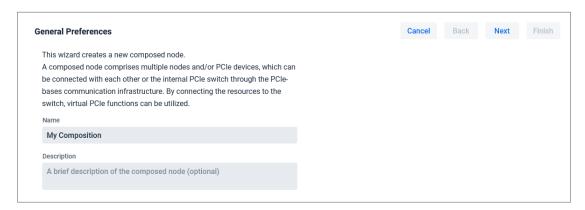

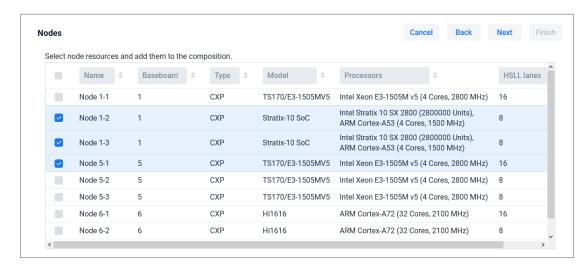

A major progression of the Web GUI within LEGaTO was its extension to support the complete node composition process in order to have this important feature embedded within the RECS|Box system without the need for an additional Open-Stack installation. Now all resources and connections between them as well as the utilization of PCIe functions can be configured easily by the user through this Web GUI. The following figures show an example node composition process with the "Node Composition Wizard" of the RECS|Box Web GUI.

After giving the new composed node a name and description in the first step (figure 3.4), the user gets a detailed list of all available microserver resources within the RECS|Box cluster server. He can now select nodes, that will be part of the composition (figure 3.5). In this example, two Intel Stratix 10 SX 2800 FPGAs from baseboard 1 and an Intel Xeon microserver from baseboard 5 are selected.

In the next step (figure 3.6) an NVIDIA Tesla V100 is selected from the available PCIe extension cards to also be part of the composed node to be created. Like the Intel Xeon node, it is connected to baseboard 5 and provides a physical and

Version 1.0 13 / 73

Figure 3.4. Node Composition Wizard - General preferences view

Figure 3.5. Node Composition Wizard – Node selection view

Figure 3.6. Node Composition Wizard – PCIe device selection view

#### a virtual PCIe function.

After that, all physical resources of the composed node to be created are selected. In the following, they will be connected and PCIe functions will be assigned.

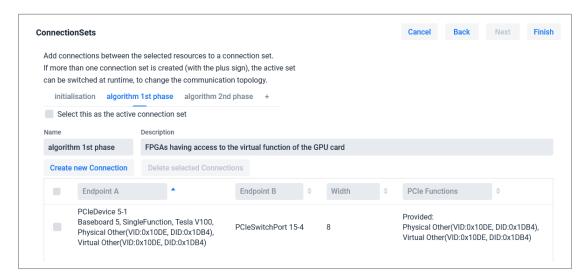

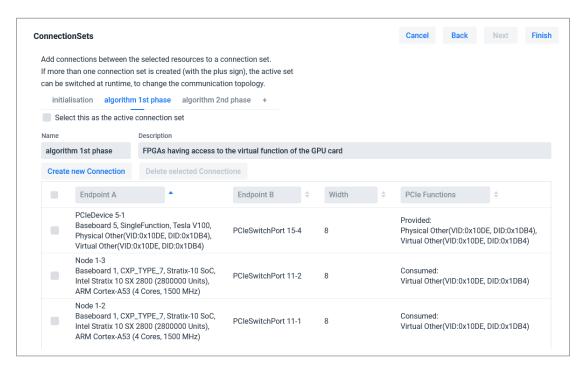

An essential part of dynamic node composition is the reconfiguration of the physical high-speed low-latency connections and PCIe functions during runtime. To achieve this, one can now specify certain independent sets of connections between the physical resources of the composed node. In this example (figure 3.7), three connection sets named "initialisation", "algorithm 1st phase" and "algorithm 2nd phase" are defined by the user within this wizard. Only one of these sets can be active at a time and each one consists of multiple connec-

Figure 3.7. Node Composition Wizard – Connection sets view

tions between the resources selected before. During runtime, the active set can be changed by calling the Redfish API (figure 3.9 in D3.2 [36]). This then results in an immediate reconfiguration of the physical high-speed low-latency infrastrcture of the RECS|Box. If one of the connection endpoints is a port of a PCIe switch, a connection can also define one or more PCIe functions, which will be shown in the following.

In this case (figure 3.7), one connection with 8 lanes will be established between the NVIDIA Tesla V100 extension card and an embedded PCIe switch port. By doing this, the switch can then extend the single-root (SR-IOV) to multi-root virtualisation (MR-IOV) and thus, expand the virtual function of the GPU extension card to be used concurrently by multiple resources connected to the switch.

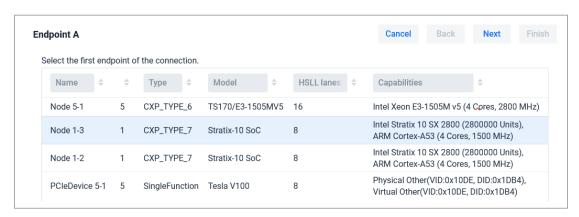

Figure 3.8. Connection Wizard – Endpoint A selection view

Now, further connections can be added to the connection set, using the virtual function provided by the NVIDIA Tesla V100 and distributed by the PCIe switch. For that matter, the "Connection Wizard" can be started to define such connection. In the first step of this wizard, the first endpoint of the connection has to be specified. In this example (figure 3.8), one of the FPGA resources is selected.

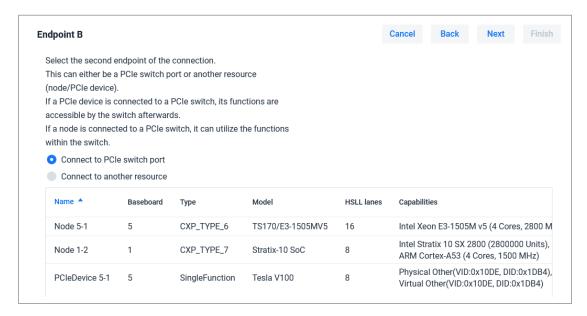

In the next step (figure 3.9), the user has to define the second endpoint of the connection. This can either be one of the other resources within the composed node or a port of PCIe switch like in our case.

Figure 3.9. Connection Wizard – Endpoint B selection view

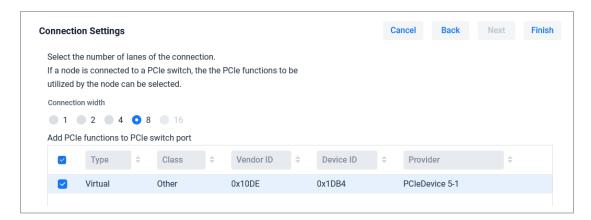

Figure 3.10. Connection Wizard – Connection settings view

By connecting the FPGA to the switch port, the number of lanes has to be specified this connection will consist of. In addition to that, all virtual PCIe functions available at the switch are listed and can be chosen from. In our case, the virtual function of the PCIe device is shown and selected. It will be added to the PCIe switch port when the connection is physically configured by activating the connection set, this connection belongs to.

After repeating this wizard with the other FPGA resource of the composed node, the connection set "algorithm 1st phase" is complete, now containing all three specified connections, which can be seen in figure 3.11.

If all connection sets are defined, the "Node Composition Wizard" can be finished. This triggers the allocation and assembling of the composed node. The underlying hardware is then configured according to the connection set marked as active (e.g. "initialisation"). After the active connection set is then switched to "algorithm 1st phase", both FPGAs will be able to concurrently use the virtual PCIe function provided by the NVIDIA Tesla V100 through the PCIe switch. When the algorithm reaches a certain point, the runtime can trigger the last connection set "algorithm 2nd phase" to have a new communication topology for a

Figure 3.11. Node Composition Wizard – Connection sets view (complete)

more efficient computation in that phase.

After the computation has finished, the composed node can be deleted directly from within the runtime by calling the Redfish API or by the user utilizing the Web GUI. This deletion will roll back all configurations and frees the assigned resources. S

#### 3.3. RECS Platform Drivers

In order to use the described node composition features from LEGaTO's runtime layer, we are developing the runtime system support for GPUs and FPGAs. For GPUs, CUDA and OpenCL already include libraries with the necessary low level services for OmpSs. On the Xilinx FPGAs, we provide the xdma and xtasks libraries that work on top of the vendor driver in Linux. We currently interoperate with the Xilinx and Alpha-Data drivers on the various Xilinx integrated and discrete FPGAs supported by the LEGaTO runtime (Zynq 7000, Zynq U+, and Virtex-7).

Since mid-2019, we have improved the quality of the information published by the bitstreams generated, and accessible on the Linux devices directory /dev/ompss\_fpga. This is a summary of the information:

- bit\_info/wrapper\_version, includes the version of the wrapper code generated for this bitstream. It is used to determine if the software side complies with the proper arguments and protocol to connect with the IP core.

- bit\_info/ait\_version, indicates that the new release of the AIT (Accelerator Integration Tool) was used to generate the bitstream instead of the former autoVivado.

- bit\_info/ait\_call, includes the command invocation and arguments

Version 1.0 17 / 73

provided to AIT. As an example, the call used in the matrix multiplication example is:

```

ait.pyc —name=matmul —board=zcu102 —c=300 —hwruntime=som

—interconnection_opt=performance —to_step=bitstream

—wrapper_version=6

```

• bit\_info/xtasks, includes the information on the generation and invocation of the IP cores. E.g., hash\_key #instances name frequency

With the bitstream information available, the xtasks library checks the compatibility of the application binary generated, with the bitstream configured in the FPGA, and the it has the features required by the application.

We have also fixed an issue related to loading and unloading the kernel module several times, that was corrupting the Linux internal data structures.

#### 3.4. SLiC API

Maxeler DFEs are accessed through the Simple Live CPU interface (SLiC) API and the MaxelerOS runtime. The SLiC API provides a shared library for host code integration. It provides the relevant function calls to interact with a DFE, such as configuring the device, setting registers, accessing memory, and streaming data. MaxelerOS provides the runtime components that include a daemon to interface with DFEs, low-level devices drivers and utilities for managing and monitoring DFEs. Both SLiC and MaxelerOS are components that are part of Maxeler's commercial toolset and they were already described in detail in Deliverable D2.1 [47].

Traditionally, Maxeler has targeted its own in-house developed DFEs with its toolset. During the LEGaTO project, Maxeler extended support to also include Xilinx Alveo U200 and U250 data center cards as compiler targets that are systemlevel compatible to Maxeler MAX5 DFEs. The SLiC API and MaxelerOS runtime were extended accordingly to support these devices. This expands the number of FPGA devices that are supported through the LEGaTO toolstack.

## 4. Energy-efficient task-based runtime

This chapter describes our efforts to develop runtime technologies targeting scalability and high energy efficiency.

#### **4.1. XiTAO**

XiTAO is a lightweight layer that provides a task-parallel and data-parallel interface using modern C++ features. The design goals of XiTAO are to be low-overhead and to serve as a development platform for testing scheduling and resource management algorithms.

#### 4.1.1. XiTAO software topologies

Software topologies is a mechanism implemented in XiTAO to achieve strict locality-aware scheduling of tasks in a portable manner. Since the execution model of XiTAO DAGs is *compile-once run-anywhere*, any information for locality aware

Version 1.0 18 / 73

scheduling needs to be generic and interpretable at runtime. At the task level, XiTAO implements a concept called "virtual topologies" which is converted at runtime into actual thread mappings to enforce locality aware scheduling. This mapping is *strict* in the sense that tasks that have a locality specification are no longer subject to load balancing. It is hence important to only use the locality feature when strictly necessary to avoid excessive communication. We will explore more relaxed schemes in the future.

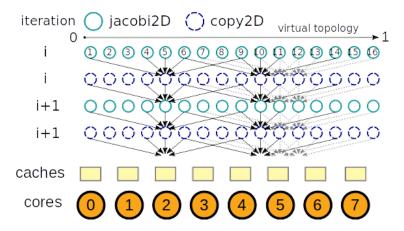

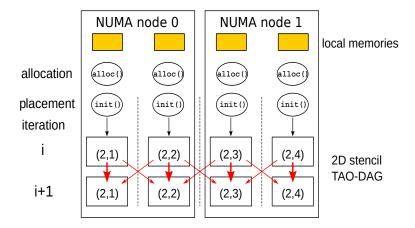

XiTAO's virtual topologies consist of regular N-dimensional cartesian topologies. Figure 4.1 shows an example with virtual mappings of the jacobi2D and copy2D kernels as implemented in the Heat benchmark that is part of the sample benchmarks available in the public XiTAO git repository. In this example, each task in the DAG of task assembly objects (TAO-DAG) is given an address (called a software topology address) in a virtual topology consisting of a one-dimensional topology (a line between o and 1). Generally, the idea is that by measuring the virtual distance between two XiTAO tasks, the runtime obtains approximate information on the communication relationship between the two tasks. If two tasks have the same address, this is understood by the runtime as meaning the highest amount of data reuse between the two tasks. As a consequence, the Xi-TAO runtime will attempt to schedule the two tasks on the same set of cores. This then optimistically results in data reuse via the caches of the cores. In the current state of XiTAO, we have implemented one-dimensional virtual topologies. As tested with the Heat diffusion simulation benchmark, this scheme can have a very positive impact on performance by avoiding unnecessary communication.

Figure 4.1. Virtual topology mapping of Jacobi2D and Copy2D kernels

XiTAO's virtual topologies can also be used to support NUMA-aware data placement. This is achieved by introducing an extra layer of tasks that takes care of data placement. Using virtual topologies, this layer of tasks can be scheduled to the same cores and NUMA nodes as the dependent tasks. This, combined with the default first touch allocation implemented in the Linux kernel<sup>1</sup>, achieves locality-aware data placement. The overall idea is shown in Figure 4.2. The first touch policy specifies that the physical memory page is allocated on the node that first writes to the data. This is important since it means that data

https://queue.acm.org/detail.cfm?id=2513149

Version 1.0 19 / 73

allocation (e.g. via malloc()) is not enough to ensure correct data placement, but in fact data placement happens when data is written to for the first time. Hence, as shown in Figure 4.2, initializing the data will take care of the proper data placement.

#### 4.1.1.1. XiTAO Virtual Places Mapping

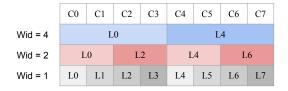

The granularity of the software topology mapping is managed by XiTAO at runtime, so rather than mapping to a single core, the runtime may decide to mold the task on more than one core within the specified locality. To aid this mapping, the hardware layout may be optionally passed to the runtime. Figure 4.3 shows a possible way to express an dual socket 8-core system. Width 4 has two place options: Co-C3 and C4-7. Such places are also candidates for STA mapping if the STA lies in either range. The runtime scheduler is designed to look for the optimal place for a task depending on an online performance model discussed in Section 4.1.2

Figure 4.2. Adding an extra layer for NUMA-aware data placement

Figure 4.3. A sample view of the hardware places uncovered by the software topology address

#### 4.1.2. The XiTAO heterogeneous scheduler

Modern multicore systems feature performance asymmetric cores to enable energy efficient execution of a variety of applications. Dynamic scheduling, such as random work stealing scheduler (RWSS), is widely used by many task-based runtime systems as the underlying scheduling strategy. RWSS greedily assigns tasks to any available resources and employs work stealing to ensure load balancing. On asymmetric platforms with more general DAGs, applying RWSS can result in suboptimal performance and inefficient utilization of resources, for example, by poorly mapping non-critical tasks to the fastest resources and vice-versa.

Version 1.0 20 / 73

Figure 4.4. Energy efficient task scheduler runtime overview.

Some recent proposals have specifically targeted the issue of energy efficient task scheduling. However, these works suffer from several shortcomings. Firstly. they do not consider per-task power characteristics, where we show that the choice of core(s) to execute a task in an energy efficient manner is primarily affected by the kernel type, for example, compute-bound, memory-bound, cachesensitive, etc. Our analysis also shows that runtime idle energy due to running the work stealing loop is significant, especially when the parallel slackness is low. Secondly, these works cannot handle intra-task (or nested) parallelism but only inter-task parallelism and instead only allow a task to run on a single core. Thirdly, these proposals rely on the assumption of fine-grained per-core DVFS control for achieving energy efficiency. However, most systems only feature cluster-level DVFS where DVFS settings can only be controlled for all the cores in the cluster but not individually. Another issue is the fact that modern power management monitoring and control introduces significant timing overheads. It was shown that DVFS transition time can last from tens of microseconds to over a millisecond [11]. However, with fine-grained tasks sized of microseconds level, the assumption of fine-grained per-task DVFS scheduling is unrealistic any more.

In LEGaTO, we propose an energy efficient task scheduler that reduces energy consumption by determining energy aware mappings for all tasks, which addresses the problem of scheduling of task-DAGs on asymmetric systems where frequencies are either fixed or managed by the OS power governors.

#### 4.1.2.1. Energy Efficient Scheduler Overview

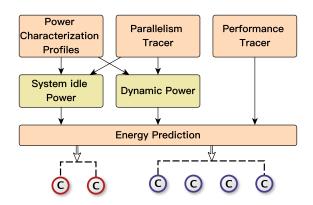

The task scheduler features several components: power characterization profiles, a performance tracer, a global parallelism tracer and a local task mapping algorithm. Figure 4.4 highlights the essential components in the proposed scheduler. These components perform the following functions: The power characterization of the platform allows the scheduler to understand CPU power consumption trends with respect to type of tasks, number/type of cores and frequencies. The performance tracer consistently tracks the history of task execution time on different cores types and counts and allows to predict the performance of future tasks given a set of resources, which is the performance trace table described in section 4.1.2 in deliveriable 3.2. The parallelism tracer gives the information of real-time parallel slackness of cores, which allows the algorithm to attribute system idle power and dynamic power to running tasks, even when some cores in the system are idle (not running any tasks). Finally, the lo-

Version 1.0 21 / 73

cal task mapping algorithm takes the system idle energy and per-task dynamic energy into account to fulfill the energy prediction for each task.

**Power Characterization Profiles**. The goal of this component is to estimate power consumption when mapping a task to an execution place. Here, we adopt offline characterization method because of the limitation of the power sensor. We consider tasks to be broadly grouped into one of the following categories: compute-bound, memory-bound and cache-sensitive. For characterization, we utilize one micro-benchmark as a representative for each category. We construct a simple power model that can provide an estimate for the power consumption of a task and is a function of execution place (leader core (LC), resource width (RW)) and task category (TC). The total power consumption  $(P_{tot})$  of a task when running at a specific frequency (F) is given by Equation 4.1:

$$P_{tot}(LC, RW, TC, F) = P_{idl} + (P_{one} + P_{oth} \cdot (RW - 1))$$

(4.1)

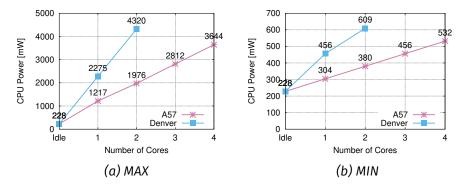

Here  $P_{idl}$  represents system idle power, which CPUs consume even when no application is running.  $P_{one}$  represents dynamic power consumption when using only one core in a cluster (resource width of one).  $P_{oth}$  represents the increase in dynamic power consumption when more than one core in the cluster is used. We carry out offline characterization on NVIDIA TX2 using two frequency levels: MAX (2,035,200 Hz) and MIN (345,600 Hz), although it can be easily extended to a broad range of other frequencies.

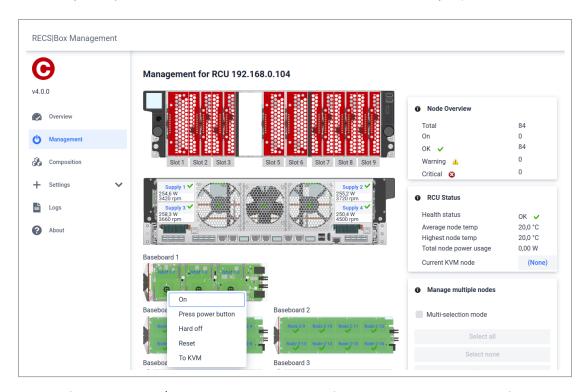

For example, Figure 4.5 shows the CPU power measurement when running the compute-bound microbenchmark with different number of cores and frequencies. When turning on all six cores while keeping them in idle state, the system idle power is found to be approximately 228 mW. We turn off the Denver cluster to measure  $P_{idl}$  of the A57 cluster, and observe it to be 152 mW. The Tegra Linux kernel does not permit powering off core zero (A57 in this case). Therefore, we can only turn off the Denver cluster. We infer that the idle power consumption of the Denver cluster is 76 mW (228 mW-152 mW). It is obvious that irrespective of the frequency, CPU dynamic power consumption linearly increases when additional cores from same cluster are used. Based on the measurements shown in Figure 4.5, we obtain the CPU power consumption profile for the compute-bound task category as shown in Table 4.1.

Figure 4.5. CPU power consumption of compute-bound microbenchmark on two clusters in MAX and MIN frequencies.

**Parallelism Tracer.** Our analysis indicates that idle threads consume considerable energy throughout execution. For example, it shows that running the

Version 1.0 22 / 73

Table 4.1. Power consumption profile of compute-bound tasks

| Cluster (C) | Frequency (F) | $P_{idl}$ | $P_{one}$ , $P_{oth}$ |

|-------------|---------------|-----------|-----------------------|

| A57         | MAX           | 152 mW    | 854 mW / core         |

| A3/         | MIN           | 152 mW    | 76 mW / core          |

| Denver      | MAX           | 76 mW     | 2046 mW / core        |

| Delivel     | MIN           | 76 mW     | 190.5 mW / core       |

worker loop on the Denver core roughly consumes 60% of the power of running a compute-bound task. While on MIN frequency, the worker loop roughly consumes up to 75% of the power of running a compute-bound task. To reduce the total energy waste, the scheduler puts cores to sleep after they make several unsuccessful steal attempts. We use an exponential backoff strategy when selecting the sleep duration for idle cores. For each sleep decision, the runtime checks a threshold parameter N, that is how many times the core has been unsuccessfully trying to steal tasks. Upon wake up, if the core finds a ready task or makes a successful steal, it resets the backoff parameter. Otherwise, it will sleep for an exponentially increasing time if it can not find ready tasks. Listing 4.1 highlights the basic implementation of this approach.

```

int idle_tries = o, backoff_param = o;

while(true){

//check local queue or try to steal

if(no_available_tasks){

idle_tries++;

if(idle_tries==N){

sleep(1<<backoff_param);

idle_tries = 0;</pre>

backoff_param++;

10

} else

11

backoff_param = o;

13

idle tries = o;

// execute task

14

15

```

**Listing 4.1** The exponential backoff sleep approach.

**Task Energy Prediction.** The prediction scheme of the energy efficient task placement for a single task is shown in Algorithm 1. The inputs include status that stores the core states (sleeping o or active 1), incoming tasks. The output is the predicted optimal task placement for each task. Line 5 shows the leader core belongs to cluster A. Through accumulating the corresponding set bits, we can obtain the number of active cores per cluster (Line 6-7). If there are any active cores on cluster B, the parallel tasks running on the cluster A share total idle power of the cluster, which can be obtained by powering off cluster B (Line 8-9). Otherwise, they share the entire board's idle power since there is no active core on cluster B (Line 10-11). Line 19 presents the resource occupation of task j over all running tasks on cluster A. Line 20 demonstrates the estimation of idle power for task j. The total dynamic power consumption of all tasks running on cluster A can be obtained by plugging the values from the corresponding power profile in the formula shown in Line 21. Line 22 involves the estimation of dynamic power by task j. Finally, we could obtain the energy consumption estimation of the task on specific configuration shown in Line 23. Line 24-27 iterate each possible

configuration until getting the optimal energy efficient placement for the task.

#### **Algorithm 1** Energy Efficient Task Placement Selection(for the case of two clusters)

```

1: Input: status, incoming task j

2: Output: optimal task placement for task j

3: Minimum = infinite

4: for each possible configuration (leader core, width) do

Leader core belongs to clusterA

6:

NumActiveCores_clusterA = accumulate(status[x-y])

NumActiveCores clusterB = accumulate(status[v-z])

7:

8:

if NumActiveCores_clusterB > o then

9:

IdleP_temp-clusterA = IdleP_tot-clusterA

10:

else

11:

IdleP_temp-clusterA = IdleP_tot

12:

Check if cores [leader, leader+width) are active

for i in leader, leader+width do

13:

14:

if status[i] is o then

15:

NumActiveCores_clusterA++

16:

Task j Resource Occupation: RO_j= width_j/NumActiveCores\_clusterA

17:

IdleP[j] = IdleP\_temp-clusterA \times RO_j

18:

DynaP_tot = P_one + P_oth × ( NumActiveCores_clusterA - 1 )

19:

DynaP[j] = DynaP_tot \times RO_j

20:

Energy = ( IdleP[j] + DynaP[j] ) × Execution Time

21:

if Energy < Minimum then

22:

Minimum = Energy

Update optimal placement with new (leader, width)

```

#### 4.1.2.2. Energy Savings Evaluation

Table 4.2. Summary of evaluated schedulers.

| Name                                      | Acronym    | Notion                                                                |

|-------------------------------------------|------------|-----------------------------------------------------------------------|

| Random Work Stealing Scheduler            | RWSS       | Typical greedy scheduler                                              |

| Random Work Stealing Scheduler with Sleep | RWSS+Sleep | RWSS enhanced with Sleep                                              |

| Fast Core Always Scheduler with Sleep     | FCAS+Sleep | Performance-oriented criticality scheduler enhanced with Sleep        |

| Low Energy Task Scheduler (D)             | LETS(D)    | The proposed scheduler prediction only using dynamic power            |

| Low Energy Task Scheduler (D+S)           | LETS(D+S)  | The proposed scheduler prediction using dynamic and system idle power |

We use an NVIDIA Jetson TX2 development board for our evaluation. The board is set to MAX-N nvpmodel mode. The benchmarks are the same like in deliveriable 3.2 section 4.1.2. All evaluated schedulers in this section are described in Table 4.2.

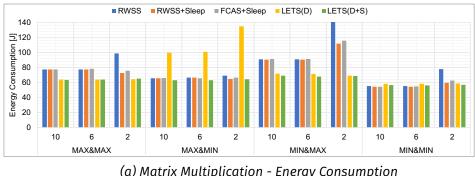

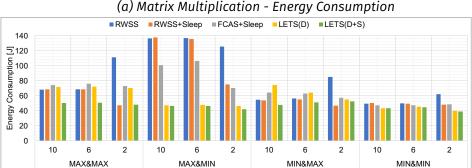

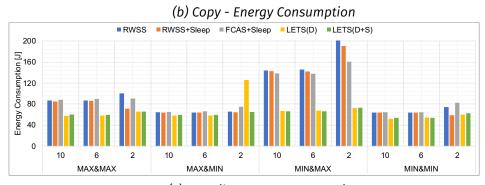

Figure 4.6 shows the total energy consumption comparison of these scheduling runtimes with or without Sleep. The results of "FCAS" without Sleep are dropped in favor of reducing clutter in the figures, as the latter delivers a relative advantage similar to "RWSS+Sleep". It is obvious that LETS(D+S) achieves the best energy savings over the other two schedulers in most of cases. Taking matrix multiplication as an example, using LETS(D+S) achieves up to approximately 25% energy savings compared to RWSS and FCAS+Sleep when the parallelism of the task DAG is high (10 and 6). With a lower parallelism of 2, LETS(D+S) achieves more energy savings which range from 6% to 60% compared to RWSS variants, and from around 4% to 40% compared to FCAS+Sleep. In the case of minimum cluster frequencies and high parallel slackness, i.e., MIN&MIN and DAG parallelism=10 or 6, the energy consumption of LETS(D+S) does not add a notable benefit (if any) since the two clusters operate at the lowest frequency, which renders the scheduling decision of no vital impact for a compute-bound kernel.

Version 1.0 24 / 73

(c) Stencil - Energy Consumption

Figure 4.6. The energy consumption comparison results of three benchmarks. The x axis includes frequency combinations and task DAG parallelism. MIN&MAX means Denver is set to MIN and A57 is set to MAX, and so on.

An important fact is that the energy consumption of LETS(D+S) is relatively stable throughout all frequency combinations as opposed to others, which means that our proposed scheduler could achieve the most energy efficient task scheduling no matter what cluster frequencies are, which implies that it is agnostic of the OS DVFS events.

#### 4.1.3. Support for Pipeline Parallelism

A significant amount of scientific applications execute the same workflow on multiple input units of same size. Such applications can be expressed as parallel pipelines by identifying the computational tasks of applications as pipeline stages. Commonly, applications expressed as a chain graphs (DAGs) are ported into parallel pipelines for efficient scheduling on multi-core computing platforms.

Pipeline paralleism is applied when a chain of tasks operate on a single input unit to produce output and there is a data dependency from task  $t_i$  to  $t_{i+1}$ . All the tasks are executed in parallel but on different input units. We implemented

Version 1.0 25 / 73

pipeline parallelism on the top of the existing XiTAO's programming model.In XiTAO, application is expressed as a DAG where each node is a standalone Task Assembly Object(TAO). A TAO can be serial or parallel. Parallel TAOs contain it's on local scheduler, the mode of parallelism inside a TAO is Data parallel. Thus XiTAO has a mixed-mode programming model. We implemented pipeline stages as a self-calling TAO (making an edge to itself).

#### 4.1.3.1. Pipeline Parallelism implemented in XiTAO

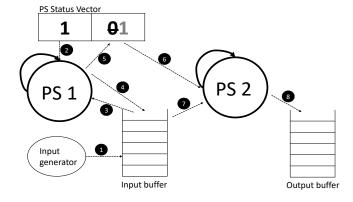

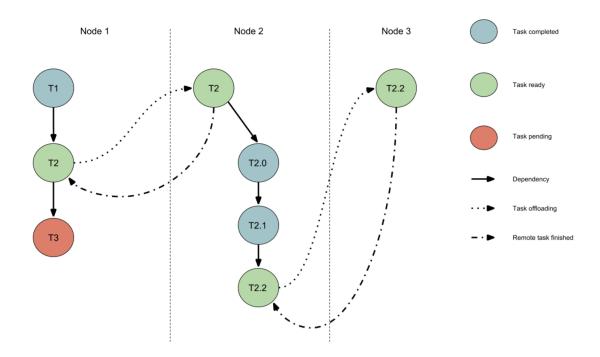

For the sake of understanding let's consider a motivating example. An application is divided into two tasks  $t_1$  and  $t_2$  such that,  $t_1$  processes an input token and produce an output. The output from  $t_1$  is fed into  $t_2$  which further processes and provides a final output. The application works on a stream of input tokens of same size. Let's define  $t_1$  and  $t_2$  as TAOs in XiTAO implementation. Ideally there is an edge from  $t_1$  to  $t_2$  but since we are implementing a pipeline, we make these TAOs a self-calling TAO. Whenever there is a ready input for pipeline stage it should execute itself and notify the successive pipeline stage when its input is ready. The mechanism of notifying successive stages about the ready input is implemented in the form of a data structure which holds the number of input units ready to be processed by corresponding pipeline stage. The mechanism is explained in Figure 4.7.

Figure 4.7. Step-by-step depiction of parallel pipeline stages in XiTAO runtime

Listing 4.2 highlight the necessary steps to implement XiTAO pipelines. Basic functionality of each pipeline stage is abstracted out from line 2 - 15. Each pipeline stage execute respective computations on input data (line 10-12) in parallel by the number of threads determined by the runtime. Once processing is done, last thread of the TAO exiting the process\_stage() computations does some boilerplate work: Notifying next stage and calling same pipeline stage again for next available input unit (Line 17 - 25). Finally in main(), we declare pipeline stages and launch only once. Note that each pipeline stage will remain active in the system until last input unit is processed by last pipeline stage. However Pipeline moldability is achieved by changing the resource width of the TAO at every call to  $xitao_push()$ .

Version 1.0 26 / 73

```

1 #define MAX_INPUTS 100

#define NUMBER_OF_PIPELINE_STAGES 2

int PS_status[NUMBER_OF_PIPELINE_STAGES];

// Define pipeline stage

5 class PipelineStage : public Assemblytask{

public: PipelineStage(int stage_number, int input_number, int batchSize){}

void execute(){

if(stage_number == 1)

process_stage1();

process_stage2();

if(is_last_thread) // Last thread finishing the work should do the job of notifying

notify_and_call();

15

16

17  void notify_and_call(){

18

//work Forwarding

if(stage_number != STAGES-1) // if it is not the last Pipeline stage

PS_Status[stage_number+1]+=1; //activate next stage for current input unit

20

//Self_calling

input_number++ // pick next work item

23

if(input number <= batchsize)</pre>

24

xitao push(new PipelineStage(stage number, input number, batchSize));

25

26

28

29 //execuet Pipeline

PipelineStage PS1 = new PipelineStage(1, 1, MAX_INPUTS);

PipelineStage PS2 = new PipelineStage(2, 1, MAX_INPUTS);

33

34 generate input stream();

PS_Status[o] = 1; //First stage is activated manually

PS_Status[1] = -1; //second stage is in active by default

xitao_push(PS1); // Launch Pipeline stage 1

38

xitao push(PS2): // Launch Pipeline stage 2

39

```

Listing 4.2 Pseudo code for implementing parallel pipeline stages in XiTAO

# 4.1.3.2. Template based Tensor-Expression Language for generating pipelined XiTAO code

For the sake of usability and expressivity, we designed a simple template based language targeting deep neural network applications. Convolutional Neural Networks (CNN) in particular consists of several convolutional layers in combination with computationally light layers such as maxpooling and softmax layers. Each layer processes on the output of previous layer and produces output for successive layer. The structure of CNNs resembles to chain graphs. Moreover inference phase of CNNs is applied on a stream of input units for example object identification in video stream. Thus CNNs are a good case for experimenting pipeline parallelism under XiTAO environment.

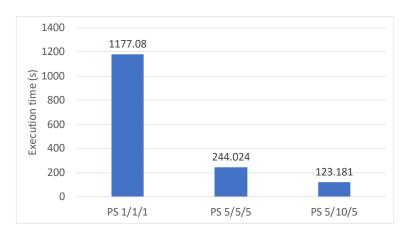

A three layered CNN [Conv1, Conv2, FC] is implemented using template based tensor expression language in Listing 4.3. layer parameters and input tensors are initialized from lines 4 to 26. Network structure is defined in lines 29 to 31. The last argument of each layer specifies the pointer to preceding layer. Once network structure is defined, we define pipeline stages for each layer at the back end. Sequence of pipeline stages is determined by the last argument of layer definitions. For example in line 30 conv1 is set as preceding layer of conv2. Line 34 launches the whole network which means pipeline stages corresponding to each layer are launched under the XiTAO runtime. Figure 4.8 shows preliminary results of the discussed approach executed on a homogeneous platform, a cluster of dual socket Intel Heswell nodes. We executed a 3-layer-CNN network. The

```

#include "PipelineStages.h"

#include "TensorExpressions.h"

const int batchSize = 10;

const int W = const int H =

const int C

const int R1 =

const int S1 =

const int C1 = const int K1 =

const int R2 = const int S2 =

const int C2 =

const int K2 =

K1;

const int R =

17

18

const int stride = 1;

const int padding = 1;

21 int main() {

Tensor<4, float > inputTensor({batchSize, H, W, C});

22

auto input = TensorExpr<4, float >(inputTensor);

23

auto w1 = Tensor<4, float >({R1, S1, C1, K1});

auto w2 = Tensor<4, float >({R2, S2, C2, K2});

auto m = Tensor<2, float >({M, R*R});

27

28

xitao_init();

29 auto conv1 = Conv2D<float > (batchSize, R1, S1, C1, K1, H, W, C1, stride, padding, w1, input);

auto conv2 = Conv2D<float > (batchSize, R2, S2, C2, K2, H, W, C2, stride, padding, W2, conv1);

30

auto result = FC<float>(batchSize, {M, R*R}, {R*R}, m, conv2);

33

xitao_start();

34

result.run();

xitao_finish();

36

37 }

return o;

```

Listing 4.3 Code for a small pipelined-XiTAO CNN

workload distribution is such that PS2 > PS1 > PS3. Since pipeline stage 2 is heavier than the other two stages, a configuration in which more cores are given to PS2 yields better execution time.

Figure 4.8. Execution time of 15 input units with different resource widths given to each pipeline stage.

#### **4.2.** OmpSs

#### 4.2.1. OmpSs@FPGA

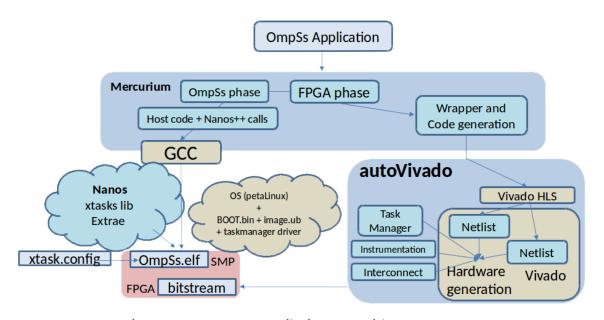

**OmpSs@FPGA** is the OmpSs programming model extension towards the support of accelerators in FPGAs. AutoVivado / AIT has gone through versions 1.4.0 to 2.0.0, and 2.2.0 in the last 9 months of the project. In this deliverable we

present OmpSs@FPGA, summarize its status presented in the previous deliverable [36], and the changes done to the runtime and compiler infrastructure related to OmpSs@FPGA in this last period of the LEGaTO project.

#### 4.2.1.1. OmpSs@FPGA description and status by mid-2019

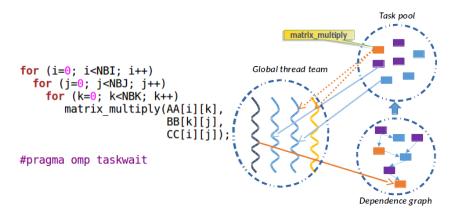

The OmpSs [40, 15] programming model allows to express parallelism that will be executed in the available resources among the host SMP cores, or integrated/discrete GPUs and/or FPGAs. OmpSs is based on task parallelism, and very similar to OpenMP tasking. It is being used as a forerunner prototyping environment for future OpenMP features. On GPUs, both CUDA and OpenCL kernels are supported. For FPGAs, OmpSs uses the vendor IP generation tools (Xilinx Vivado and Vivado HLS [33, 50], or Altera Quartus [24]), to generate the hardware configuration from high-level code. OmpSs@FPGA can also leverage existing IP cores, provided they adhere to the same interface with our software platform.

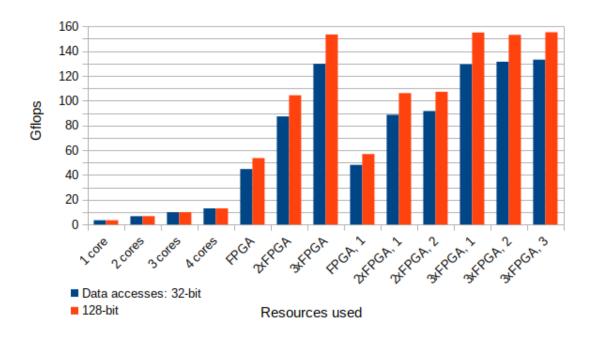

OmpSs@FPGA is a significant upgrade of the OmpSs infrastructure (Mercurium source-to-source compiler and Nanos++ runtime) to incorporate FPGA support. Figure 4.9 shows an example of an OmpSs application. In particular, function matrix\_multiply is defined as a task with input dependencies a and b and input/output dependency c. Each call to this function will be converted in a task that will be run when its dependencies are ready. This task has also been defined to be potentially executed in two target devices: any of the cores of the smp running the application and three instances of an accelerator that will be built to do this task in the FPGA. The accelerator has been tuned by the programmer to exploit the parallelism of the FPGA by using some additional directives (#pragma HLS) not related to OmpSs programming model. In the following sections, we will describe how the OmpSs compilation and runtime ecosystem helps programmability, heterogeneity, memory transfers and tracing support, and finally, mechanisms to develop blocking techniques from inside the FPGA.

Figure 4.10 shows the toolchain flow. In particular, it currently supports Xilinx FPGAs using the Vivado HLS and Vivado tools through our *autoVivado* tool.