# D3.4 "REPORT ON EVALUATION AND OPTIMIZATIONS IN THE RUNTIME STACK"

Version 1.0

# **Document Information**

| Contract Number      | 780681                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Project Website      | https://legato-project.eu/                                                                                                                                                                                                                                                                    |  |  |  |

| Contractual Deadline | 02 Nov 2020                                                                                                                                                                                                                                                                                   |  |  |  |

| Dissemination Level  | Public                                                                                                                                                                                                                                                                                        |  |  |  |

| Nature               | Report                                                                                                                                                                                                                                                                                        |  |  |  |

| Author               | Miquel Pericàs (CHALMERS)                                                                                                                                                                                                                                                                     |  |  |  |

| Contributors         | Do Le Quoc (TUD), Xavier Martorell (BSC), Leonardo<br>Bautista-Gomez (BSC), Behzad Salami (BSC), Miquel Pericàs<br>(CHALMERS), Mustafa Abduljabbar (CHALMERS), Pirah Noor<br>Soomro (CHALMERS), Jing Chen (CHALMERS), Gunnar<br>Billung-Meyer (CHR), Saber Nabavi (BSC), Paul Carpenter (BSC) |  |  |  |

|                      | Valerio Schiavoni (UNINE), Nils Voss (Maxeler)                                                                                                                                                                                                                                                |  |  |  |

The LEGaTO project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement No 780681.

# Change Log

| Version | Description of Change                                          |

|---------|----------------------------------------------------------------|

| 1539    | 2020-10-23, File created                                       |

|         | 2020-10-27, Intro to FPGA checkpointing                        |

| 1553    | 2020-10-27, FPGA undervolting results                          |

| 1569    | 2020-10-28, SGX framework comparison added                     |

| 1583    | 2020-10-29, Add XiTAO energy and pipeline parallelism results  |

| 1589    | 2020-10-30, Add XiTAO topologies evaluation                    |

| 1620    | 2020-11-03, Add execute summary                                |

| 1646    | 2020-11-06, List Valerio as a reviewer and update exec summary |

| 1672    | 2020-11-10, Add an introduction                                |

| 1679    | 2020-11-11, Update the introduction                            |

| 1680    | 2020-11-11, Conclude the final deliverable                     |

|         | 2020-11-12, Include the SLRUM-RECS integration                 |

| 1691    | 2020-11-12, Update introduction and summary to reflect changes |

| 1831    | 2020-11-30, Apply internal edits by Osman                      |

This log reflects actual revision numbers from SVN (version control software used).

# Index

| 1 | Exec  | cutive S  | ummary                                                   |

|---|-------|-----------|----------------------------------------------------------|

| 2 | Intro | oductio   | n                                                        |

| 3 | Mide  | dleware   | integration and improvement                              |

|   | 3.1   |           | 1 integration with the middleware                        |

|   |       | 3.1.1     | Slurm configuration                                      |

|   |       | 3.1.2     | Job descriptions                                         |

|   |       | 3.1.3     | Job flow                                                 |

|   | 3.2   | Improv    | vement of hardware management and APIs                   |

| 4 | Ener  | rgy-effic | cient task-based runtime                                 |

|   | 4.1   | Xitao     |                                                          |

|   |       | 4.1.1     | Evaluation of XiTAO Software Topologies 13               |

|   |       | 4.1.2     | The XiTAO heterogeneous scheduler                        |

|   |       | 4.1.3     | Support for Pipeline Parallelism 20                      |

|   |       | 4.1.4     | Pipelined execution of VGG-16                            |

|   | 4.2   |           | s                                                        |

|   | -     | 4.2.1     | OmpSs@FPGA, OpenCL and CUDA                              |

|   |       | 4.2.2     | OmpSs@Cluster                                            |

|   |       | 4.2.3     | Smart-Mirror/OmpSs@Cluster 26                            |

| 5 | Run   | time su   | pport for Fault Tolerance and Security <b>30</b>         |

| 5 | 5.1   |           | Checkpointing                                            |

|   | 5     | 5.1.1     | Host-based Checkpointing                                 |

|   |       | 5.1.2     | Checkpointing partial work of the FPGA task              |

|   |       | 5.1.3     | Environment                                              |

|   |       | 5.1.4     | Applications                                             |

|   |       | 5.1.5     | Host-Based FTI                                           |

|   |       | 5.1.6     | Partial FPGA Task Checkpointing                          |

|   | 5.2   | 0         | volting High-Bandwidth Memories                          |

|   | J.2   | 5.2.1     | Structure of HBM         40                              |

|   |       | 5.2.2     | Hardware Under Test                                      |

|   |       | 5.2.3     | Power Measurement                                        |

|   |       | 5.2.4     | Reliability Analysis Through Accessing Data Sequentially |

|   |       | 5.2.5     | Reliability Analysis Per Pseudo Channel                  |

|   | 5.3   |           | GX Framework Comparison                                  |

|   | J•J   | 5.3.1     | Performance Comparison                                   |

|   |       | 5.3.2     | Performance Metrics Analytics                            |

| ~ |       |           |                                                          |

| 6 | Con   | clusion   |                                                          |

| 7 | References |  |  | • • | ••• |  |  |  |  |  | • | ••• |  | • | ••• |  | • |  | • |  | • | • |  | • | • | ••• | 5 | 2 |

|---|------------|--|--|-----|-----|--|--|--|--|--|---|-----|--|---|-----|--|---|--|---|--|---|---|--|---|---|-----|---|---|

|---|------------|--|--|-----|-----|--|--|--|--|--|---|-----|--|---|-----|--|---|--|---|--|---|---|--|---|---|-----|---|---|

# List of Figures

| 3.1  | Job description, submission to slurm, and interaction with RECS Master                  | 12 |

|------|-----------------------------------------------------------------------------------------|----|

| 3.2  | Web-GUI of the RECS_Master in new design                                                | 13 |

| 4.1  | Sample dependency graphs for the analyzed applications                                  | 14 |

| 4.2  | SparseLU parallel execution time on 8x6-core AMD - Abu Dhabi and 4x18-core Intel        |    |

|      | Broadwell as you increase the task input size in bytes. Matrix size = 128 x 128 blocks. | 15 |

| 4.3  | Time to solution for different mesh sizes to compute 5-point stencil on two archi-      |    |

|      | tectures. Iteration count = 2000                                                        | 16 |

| 4.4  | Comparison of the cumulative work/other distribution, and the scheduling trace          |    |

|      | for a Stencil (compute and copy) tasks. The denoted tasks have a single software        |    |

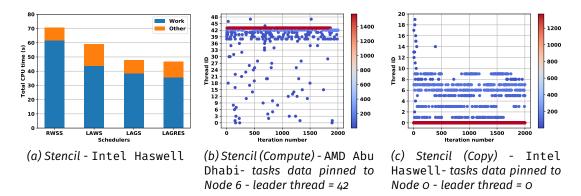

|      | topology address. Mesh resolution = $2048 \times 2048$ .                                | 16 |

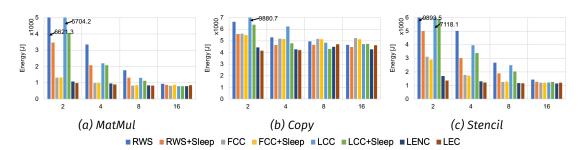

| 4.5  | Energy comparison of three synthetic benchmarks on Intel Haswell                        | 18 |

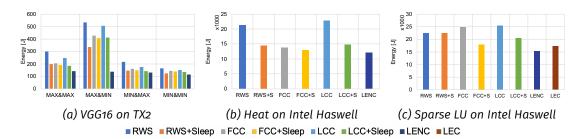

| 4.6  | Energy comparison results of three applications on two platforms. MAX & MIN in          |    |

|      | x-axis of Figure 4.6a means that on TX2 Denver cluster's frequency is maximum           |    |

|      | and A57 cluster's frequency is minimum                                                  | 19 |

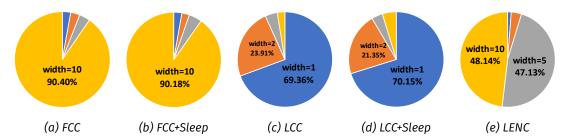

| 4.7  | Heat task distribution with different resource width on Intel Haswell                   | 20 |

| 4.8  | Overview of Pipelined CNN in XiTAO.                                                     | 20 |

| 4.9  | Execution timeline of VGG 16 on Nvidia Jetson TX2.                                      | 21 |

| 4.10 | Performance of OmpSs@OpenCL/CUDA Matrix Multiplication on the Intel Arria 10            |    |

|      | FPGA and the Nvidia GeForce GTX Titan X GPU                                             | 23 |

| 4.11 | Performance of OmpSs@OpenCL/CUDA Matrix Multiplication on the Intel Stratix             |    |

|      | 10 FPGA and the Nvidia GeForce RTX 2070 SUPER GPU                                       | 24 |

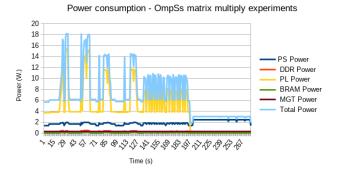

| 4.12 | Online power consumption on the matmul experiments with OmpSs@FPGA                      | 25 |

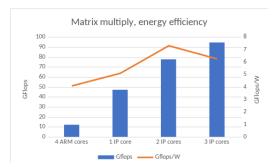

| 4.13 | Performance and energy-efficiency with OmpSs@FPGA matrix multiplication                 | 25 |

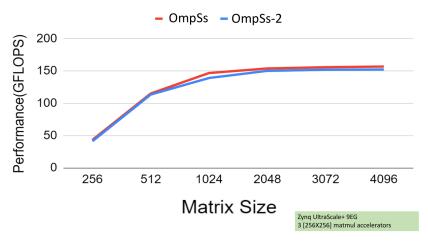

| 4.14 | Comparison of the performance of OmpSs-1 and OmpSs-2 matrix multiplication on           |    |

|      | the ZCU102 FPGA development kit, with the new OmpSs-2 directory/cache support           | 26 |

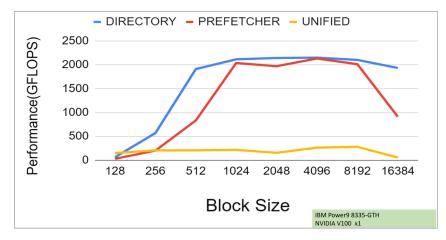

| 4.15 | Comparison of the performance of OmpSs-2 matrix multiplication, with the new            |    |

|      | OmpSs-2 directory/cache support, OmpSs-2 with Prefetching and OmpSs-2 with              |    |

|      | Unified Memory                                                                          | 26 |

|      | Single node implementation of the object detection part of the smart mirror             | 28 |

| 4.17 | Initialization step of the OmpSs-2@Cluster implementation of of the object de-          |    |

|      | tection part of the smart mirror.                                                       | 28 |

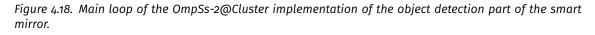

| 4.18 | Main loop of the OmpSs-2@Cluster implementation of the object detection part            |    |

|      | of the smart mirror                                                                     | 29 |

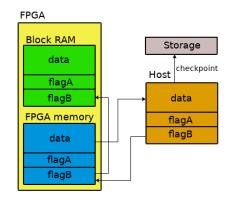

| 5.1  | Example of host-based checkpointing                                                     | 32 |

| 5.2  | Implementation of Host-based checkpointing for the Jacobi Solver application            | 32 |

| 5.3  | FPGA copies data to memory.                                                             | 33 |

| 5.4  | Host performs a checkpoint of partial FPGA data.                                        | 33 |

| 5.5  | Implementation of Partial work Checkpointing for the Jacobi Solver application          | 34 |

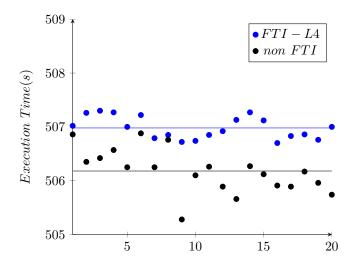

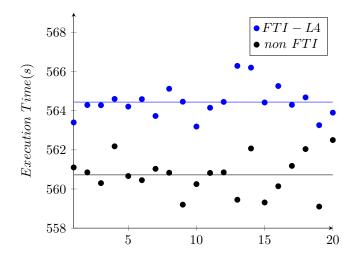

| 5.6   | Performance comparison of Jacobi Solver implementation with FTI using L4 check-                    |    |

|-------|----------------------------------------------------------------------------------------------------|----|

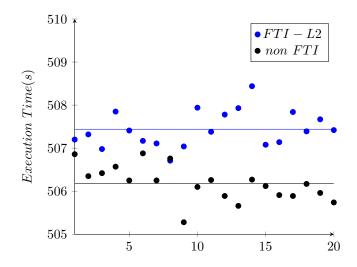

| 5.7   | point and without FTI support                                                                      | 37 |

|       | point and without FTI support                                                                      | 38 |

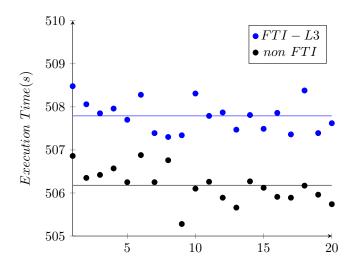

| 5.8   | Performance comparison of Jacobi Solver implementation with FTI using L3 check-                    |    |

|       | point and without FTI support                                                                      | 38 |

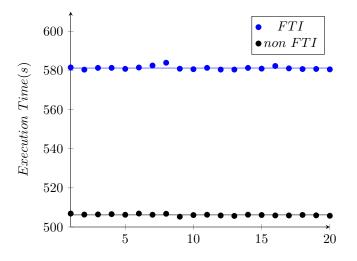

| 5.9   | Performance comparison of YUV Filter implementations with and without FTI sup-                     |    |

|       | port                                                                                               | 39 |

| 5.10  | Performance comparison of Jacobi Solver implementation with partial FPGA task                      |    |

|       | checkpointing and the non-FTI version                                                              | 39 |

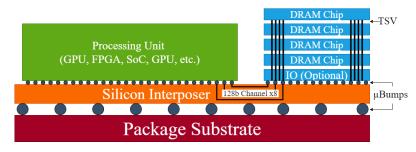

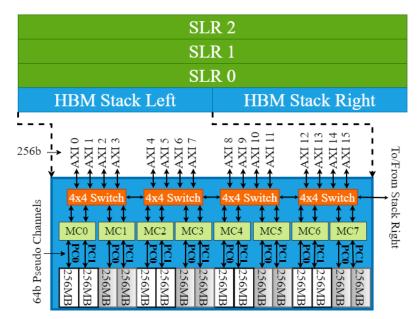

| 5.11  | General structure of an HBM-enabled Device.                                                        | 41 |

| 5.12  | HBM Interface and internal organization of XCVU37P.                                                | 41 |

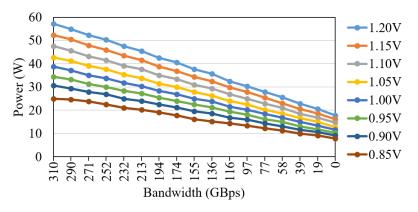

| 5.13  | HBM stack power saving by undervolting (nominal voltage is 1.2V)                                   | 43 |

| 5.14  | Operating current of HBM by undervolting (nominal voltage is 1.2V)                                 | 43 |

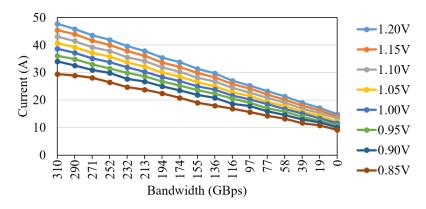

| 5.15  | Active portion of the memory under load. Vertical axis shows how much capaci-                      |    |

|       | tance is being charged/discharged every second.                                                    | 43 |

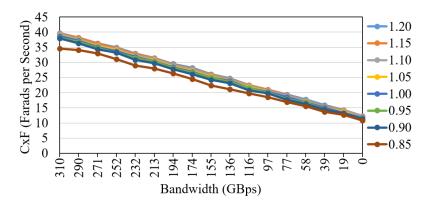

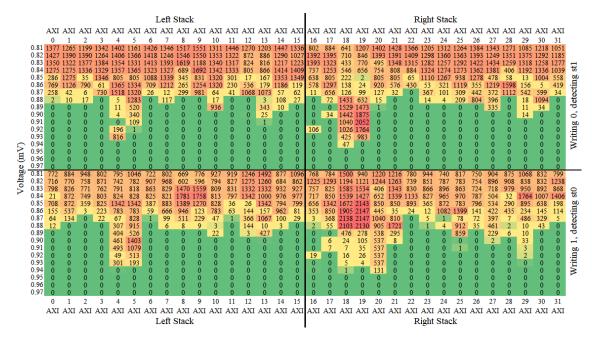

|       | Percent of data bits in each stack that are st1 or st0 with undervolting.                          | 44 |

| 5.17  |                                                                                                    |    |

|       | for st1 and bottom half is for st0. Lower numbers mean a portion of memory is                      |    |

| 0     | healthier and more reliable.                                                                       | 45 |

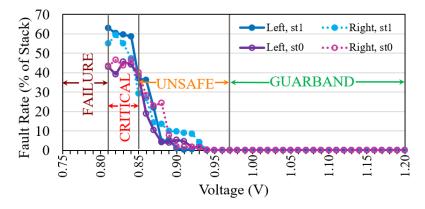

| 5.18  | Number of PCs that can be used under different thresholds (showing the sum of                      |    |

| E 40  | sto and st1 faults). Bigger numbers mean larger portions of memory are accessible.                 | 40 |

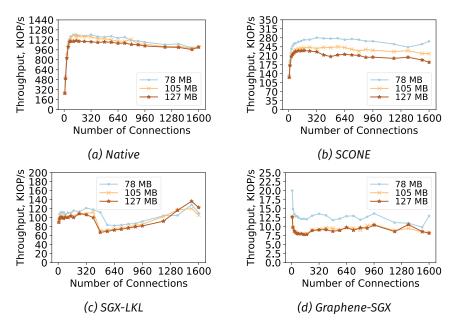

| 5.19  | The throughput comparison between native Redis and Redis with different SGX                        |    |

|       | frameworks. The total memory usage of Redis is set to different sizes of 78 MB, 105 MB, and 127 MB | 48 |

| F 20  | The latency comparison between native Redis and Redis with different SGX frame-                    | 40 |

| 5.20  | works. The total memory usage of Redis is set to different sizes of 78 MB, 105 MB,                 |    |

|       | and 127 MB                                                                                         | 48 |

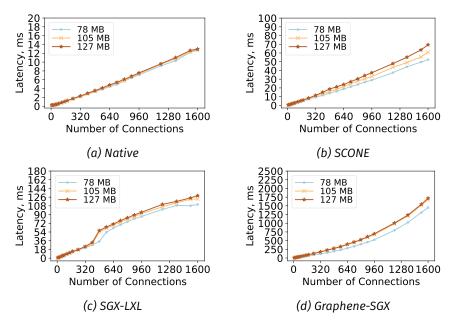

| 5.21  | The throughput and latency comparison between native Redis and Redis with dif-                     | 40 |

| J.2 I | ferent SGX-frameworks. The total memory usage of Redis is set to 78 MB.                            | 48 |

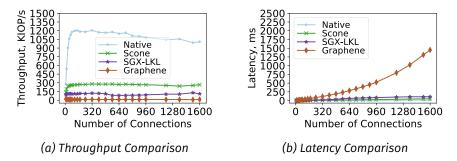

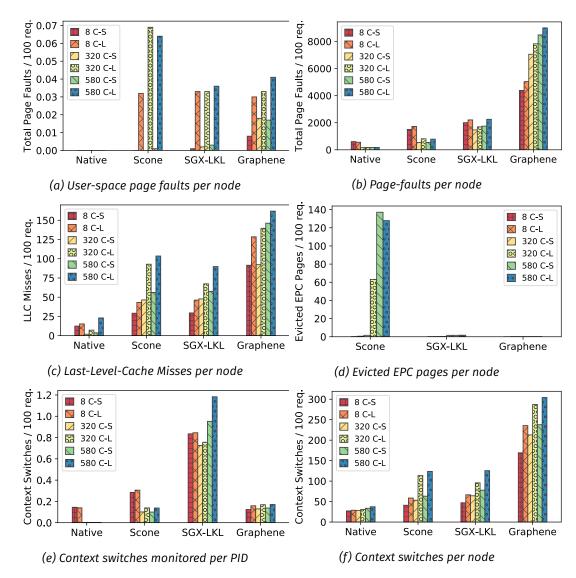

| 5 22  | The detailed statistics of monitored performance metrics of native Redis and Re-                   | 40 |

| 5.22  | dis running inside SGX enclaves using different SGX frameworks. The experiments                    |    |

|       | are conducted with different configurations: 8 connections and 78 MB database                      |    |

|       | size (8 C-S); 8 connections and 105 MB database size (8 C-L); 320 connections and                  |    |

|       | 78 MB database size (320 C-S); 320 connections and 105 MB database size (320 C-L);                 |    |

|       | 580 connections and 78 MB database size (580 C-S); and for 580 connections and                     |    |

|       | 105 MB database size (580 C-L).                                                                    | 49 |

# List of Tables

| 4.1 | Hardware structure of the used machines. In parenthesis: number of hardware  |    |

|-----|------------------------------------------------------------------------------|----|

|     | threads that share memory/cache                                              | 13 |

| 4.2 | Summary of evaluated runtime strategies                                      | 18 |

| 4.3 | CPU and GPU utilization of the single node and the OmpSs-2@Cluster implemen- |    |

|     | tations running alone                                                        | 30 |

| 4.4 | Frame rate and power consumption of whole smart mirror application           | 30 |

# 1. Executive Summary

In this deliverable, we highlight the evaluations and optimizations on top of the final release of the LEGaTO backend and middleware.

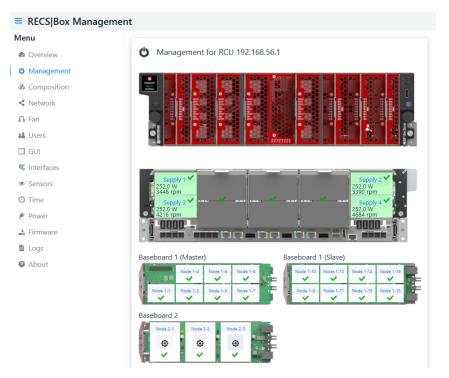

On the middleware side, we have integrated the Slurm workload manager with the RECS Master. This approach allows users to request resources using Slurm for jobs to be run in the cluster. Also, more resilience against data loss and enhanced reconfiguration capabilities have been promoted in the case of a power shutdown of the RECs box server.

In the backend, XiTAO software topologies have been validated using SparseLU and Heat diffusion benchmarks, and have shown adaptivity and consistent speedup compared to traditional locality-aware and work-stealing schemes. Thorough energy-efficient scheduling evaluation is presented for VGG16, Heat and SparseLU. The evaluation is carried out on both asymmetric and symmetric platforms, and is compared to energy-efficient and work-stealing schedulers. Overall, from 31% to 75% energy reduction is achieved in comparison to the baseline schedulers.

Further optimizations are developed on top of OmpSs backend. The performance of OmpSs@FPGA and CUDA is showcased for dense matrix multiply that appears in applications such as Convolutional Neural Networks (CNNs). Comparison of energy/performance gains using the Xilinx ZCU102 development kit have shown an efficiency of up to 7.32 GFlops/W using 2xIP core instances. The distributed variant of the OmpSs, *i.e.*, OmpSs@Cluster is evaluated using the Smart-Mirror use-case. Both the single and OmpSs-2@Cluster implementations hit the limit frame rate of the camera, which is 30 FPS. The energy consumption was 25W for the single node implementation, using the OmpSs-2@Cluster this dropped to 13W for the first node of which 10W is used for the processing of the raw captured image (*i.e.* scaling), and total of 17W for the second Xavier node.

Several evaluations of fault tolerance techniques are presented. Undervolting is demonstrated as an effective energy saving technique. Previously we had focused on the SRAM-based memories of FPGAs, while in this deliverable we extend this work to include High-Bandwidth Memory (HBM). Experimental results show a 2.3× energy saving for HBM at all bandwidth utilizations. The checkpointing library is now capable of checkpointing CPU, GPU and FPGAs under the same API in a completely transparent fashion. It has demonstrated the low-overhead of our approach, making heterogeneous computing more resilient and fault-tolerant. Last but not least, we provide an extensive performance comparison between state-of-the-art Intel SGX frameworks using our monitoring tool TEEMon, the first continuous performance monitoring and analysis tool for TEE-based applications.

By combining the various techniques introduced at the runtime and firmware levels in deliverables D3.3 and D3.4, we can achieve an order of magnitude reduction in energy consumption. Hence, we are confident that the energy efficiency goals of LEGaTO have been achieved.

# 2. Introduction

In the previous deliverables of work package 3 "Tool-Chain Back-End", we have motivated and described the implementations behind the LEGaTO task-based runtime environments on heterogeneous platforms featuring asymmetric CPUs, GPUs and FPGAs. These implementations target achieving up to  $10 \times$  energy efficiency on the next generation IoT, Edge and HPC applications, as well as addressing security and fault-tolerance concerns. Thanks to the enhanced middleware interface, the reconfigurable hardware resources provided by Maxeler and Christmann are available to validate the backend contributions. Therefore in this final deliverable, we report on evaluations and optimizations for energy-efficiency, security, and resilience on top of the final release of the task-based runtime (D3.3 [25]). In general, this document highlights

- 1. Optimizations added to techniques described in D3.3,

- 2. Detailed evaluation of techniques from D3.3 or the new optimizations developed after D3.3, and

- 3. Incremental proposals that pertain to the parts in D3.3.

In Section 3.1, we describe and showcase the Slurm-RECS integration, which makes the heterogeneous LEGaTO hardware resources available to the de facto scalable cluster management and job scheduling utility. Section 3.2 demonstrates the robustness and usability of the RECS\_Master management software and RedFish API to facilitate integration with the LEGaTO backend.

Section 4 focuses on the two runtimes researched in LEGaTO: the experimental XiTAO runtime and the production OmpSs runtime. We start by listing the optimizations and evaluations of the XiTAO backend in Section 4.1. These include an evaluation of the XiTAO topologies made available through dynamic locality-aware scheduling. Further, we include a thorough analysis of the energy-aware scheduler (EAS) as well as the pipeline parallelism. The techniques have been applied on representative HPC and machine learning benchmarks, running on an edge NVIDIA TX2 development board, one of the target platforms of the LEGaTO project.

The energy efficiency of the OmpSs backend is evaluated in Section 4.2. Starting with section 4.2.1, we evaluate OmpSs@FPGA & CUDA by executing a set of matrix multiplication experiments on the Xilinx ZCU102 development kit, with 4 ARM A53 cores and an integrated XCZU9EG FPGA. Each matrix multiplication experiment consists of 20 executions of matrix multiply operations, on a matrix of 2816x2816 single precision floating point elements. The matrix is blocked in tiles of 256x256 values. Insights are made about the performance/energy tradeoffs when tuning the amount of IP and CPU resources allocated to the described workload. The OmpSs-2@Cluster implementation is analyzed using the Smart Mirror use case in Section 4.2.2. OmpSs-2@cluster allows the CPU and GPU compute to be divided among two nodes to increase the frame rate with relatively lower increase in power consumption. This was possible using the annotations described in Section 4.2.3.2 at minimal development cost.

Section 5.1 gives more detail on the methodology followed to implement FPGA checkpointing. The work is separated into two different main approaches when it comes to implementing FTI functionality: host-based checkpointing and checkpointing of partial data from the FPGA task. We perform the experiments on a cluster of 4 Xilinx Zynq-7000 SoC nodes via the OmpSs@FPGA

environment. Comparisons by enabling and disabling the Fault Tolerance Interface (FTI) library are performed for YUV filter, Jacobi Solver and K-Means Clustering.

Then, in Section 5.2, we focus on undervolting High-Bandwidth Memory (HBM). It is known that modern high-performance devices employ HBM in order to meet high memory bandwidth requirements, but consume a substantial portion of the chip's power budget. By means of undervolting, our measurements show that the guard-band region in our HBM modules is 19% of the nominal voltage; bringing the supply voltage down to that region provides a  $1.5 \times$  power saving gain for all bandwidth utilizations. Pushing voltage down further by 11% provides  $2.3 \times$  power saving at the cost of unwanted bit flips. We explore and characterize the rate and type of these bit flips and show that the majority of them are clustered together in less than 16% of the memory's entire address space.

Finally, Section 5.3 analyzes the overheads by the developed security mechanisms based on TEEs, *e.g.*, Intel SGX or ARM TrustZone. The performance monitoring framework TEEMon [16], which has been reported in Deliverable D4.2, is used to measure the overhead of Intel SGX frameworks such as SGX-LKL [26], and Graphene-SGX [29] and as well as our own toolchain SCONE [4]. The depicted performance metrics are helpful for developers using the SGX framework in order to identify performance bottlenecks especially considering scarce resources such as EPC (Enclave Page Cache) memory and the expensive enclave exit and enter operations (due to system calls).

# 3. Middleware integration and improvement

# 3.1. SLURM integration with the middleware

We have integrated the Slurm workload manager [32] with the RECS Master service. This approach allows users to request resources using Slurm for jobs to run in the cluster. The Slurm manager selects the nodes where jobs can be run, starts the nodes, run the jobs, and stops the nodes upon completion. After that, the nodes can be used by the next job submitted.

# 3.1.1. Slurm configuration

The configuration of Slurm is provided in the etc/slurm.conf file. It provides the list of nodes available in each baseboard, and their hardware characteristics, that will be used in user jobs to decide which nodes should be selected. A baseboard is one of the slots available in the hardware system to allocate each one of the computing nodes. This information can be obtained at installation time, by using the Redfish API to obtain the hardware inventory information available in the target system.

For example, in a common Slurm file, we have:

- NodeName=BB\_1\_[0,2-15] Sockets=1 CoresPerSocket=4 ThreadsPerCore=1 Feature=ARM,bigLITTLE,hasGPU

- NodeName=BB\_2\_[0-7] Sockets=2 CoresPerSocket=2 ThreadsPerCore=1 Feature=x86\_64

It describes a collection of 15 nodes, named BB\_1\_0 to BB\_1\_15, with the exception of the nonexisting BB\_1\_1. Those nodes have 1 socket (chip), with 4 ARM cores, and a single thread per core. Additionally, each core has several big cores and additional LITTLE cores, and hosts a GPU. The Slurm features are arbitrarily set per organization, so they are adapted to the target environment.

The second collection of nodes (BB\_2\_0 to BB\_2\_7) have 2 sockets with 2 cores per socket, and their hardware architecture is x86\_64.

The Slurm configuration file also groups nodes in partitions:

PartitionName=debug Nodes=BB\_1\_0,BB\_1\_[2-15],BB\_[13-18]\_[0-7] OverSubscribe=EXCLUSIVE Default=YES MaxTime=INFINITE

This describes the *debug* partition, with the collections of nodes BB\_1\_\*, BB\_13\_\* to BB\_18\_\*, not allowing oversubscribing, and with no execution time limit.

# 3.1.2. Job descriptions

Slurm jobs are annotated with the node characteristics requested. In order to do this we use the Slurm node features specified above in the node definitions, through the *constraint* field:

```

#!/bin/bash

#SBATCH -N 4

#SBATCH --constraint=ARM

#SBATCH -o test-%j.out

#SBATCH -e test-%j.err

... job commands ...

```

### 3.1.3. Job flow

Nodes are turned off by default. When a job is submitted, Slurm takes care of selecting the nodes to be awakened and powers them up using the Redfish API. Once they are up and ready (running the slurm daemon), the job is launched. At job termination, and after a short idle period, the nodes are shutdown, and stay off till they receive a new job assignment.

This is implemented with a series of scrips executed by slurm, that contact the RECS|Box management system through its webservice. Figure 3.1 shows the high-level view of this environment.

The user submits slurm jobs using batch job scripts specifying the desired conditions that the nodes must accomplish. In the example, the user requests nodes that are described as ARM, bigLITTLE, and hasGPU. Slurm contacts the RECS Master server to power up and run the jobs. The user can follow the job execution using the Slurm tools. *squeue* shows the jobs enqueued, some of which may be running, others waiting for resources. Finally, *sinfo* that shows the partitions available, and the state of the nodes belonging to them.

# 3.2. Improvement of hardware management and APIs

In the course of the middleware evaluation, its robustness and usability were continuously improved to allow a seamless integration with the rest of the stack.

The RECS\_Master management software is the main authority for controlling the hardware resources and communication infrastructure within the RECS|Box and t.RECS servers. Therefore, it is also responsible for configuring the Ethernet and PCIe switches to separate the network between the microservers with VLANs and compose nodes by managing PCIe functions, respectively. In contrast to all other data held by the RECS\_Master, the VLAN and PCIe configuration are no physical property of the hardware and thus volatile in terms of power loss. Hence, the configuration data has to be persisted to be recovered after the power is back again. While the obvious

| #SBATCH                                                                                    | -N 10<br> constraint=ARM,<br>  -o test-%j.out<br>  -e test-%j.err       | urm job scr<br>bigLITTLE,ha                     |                            | s              | CSJBox RCU<br>tatus: OK<br>2.168.1.34 |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|----------------------------|----------------|---------------------------------------|

| \$ sbatch batch-10-bl.s<br>Submitted batch job<br>\$ squeue<br>JOBID PARTITION<br>39 debug |                                                                         | ST TIME I                                       | NODES NODE<br>10 BB_1_[0,2 | ELIST(REASON)  |                                       |

|                                                                                            | \$ sinfo<br>PARTITION AVAI<br>desktop up<br><b>debug up</b><br>debug up | L TIMELIMIT<br>infinite<br>infinite<br>infinite | NODES STA<br>2 idl         | oc BB_1_[0,2-1 | ktop2<br>0]                           |

Figure 3.1. Job description, submission to slurm, and interaction with RECS Master

and common reason for power-loss is a reboot or shutdown of the RECS|Box or t.RECS platforms, the former system has a second cause. Due to its blade-like architecture, the RECS|Box allows hot-plugging whole baseboards with multiple microservers and dedicated communication infrastructure on it. Both scenarios are now protected against data loss by persisting volatile information. When the power is on again, the RECS\_Master reconfigures all Ethernet and PCIe switches of a baseboard or the whole system by controlling the firmware layer. That way, the VLAN configuration and composed nodes are in the same state as before the power loss. In addition, the whole Ethernet management architecture within the RECS\_Master and firmware was reworked, by building a fabric over all Ethernet switches within the RECS|Box and only presenting one virtual switch to the upper layers through the Redfish API and WebGUI.

The Redfish API was also revised by changing the internal generation of endpoint URLs. This was done with regard to an easier maintenance and testability of the implementation within the RECS\_Master and a more consistent presentation to the upper layers and users of the API. Before this rework, some resources had more than one endpoint URL depending on the context it was in. One example is the high-speed/low-latency interface, which is the physical part of a microserver, PCIe device or PCIe port, where it connects to the high-speed/low-latency communication infrastructure, analogue to an Ethernet interface. Within the node composition process, those interfaces can also be the endpoints of a configured connection. Before the rework of the URL handling, such an interface could be called by two different URLs. This was now changed by assigning only one unique URL to a resource, which corresponds to its physical affiliation. The complete documentation of the Redfish API implementation of the RECS\_Master can be accessed online at Github [12].

Furthermore, the whole Web-GUI of the RECS\_Master was re-designed, now supporting recent Java versions. The main framework for the web interface, Vaadin<sup>1</sup>, was also upgraded from version 7 to 17, because version 7 was end-of-life. The new Web-GUI now conforms to more modern web standards and features responsive design, for a smoother user experience (see 3.2).

# 4. Energy-efficient task-based runtime

This chapter describes our efforts to develop runtime technologies targeting scalability and high energy-efficiency. We present the approach taken using the XiTAO runtime first, and then the developments and evaluation using OmpSs.

<sup>1</sup>https://vaadin.com/

Figure 3.2. Web-GUI of the RECS\_Master in new design

Table 4.1. Hardware structure of the used machines. In parenthesis: number of hardware threads that share memory/cache.

| Architecture    | Sockets          | Cores/socket | Threads/core | Memory(GB) | L3(MB) | L2(KB)  | L1d(KB) |

|-----------------|------------------|--------------|--------------|------------|--------|---------|---------|

| AMD Abu Dhabi   | 4 - 2 nodes each | 6            | 2            | 8(6)       | 6(6)   | 2048(2) | 16(1)   |

| Intel Broadwell | 4                | 18           | 1            | 768(18)    | 45(18) | 256(1)  | 32(1)   |

| Intel Haswell   | 2                | 10           | 1            | 256(10)    | 24(10) | 256(1)  | 32(1)   |

# 4.1. XiTAO

XiTAO is a lightweight layer that provides a task-parallel and data-parallel interface using modern C++ features. It serves as a backend runtime along side OmpSs in the LEGaTO toolchain. As mentioned in D3.3 [25], the design goals of XiTAO are to be low-overhead and to serve as a development platform for testing scheduling and resource management algorithms.

# 4.1.1. Evaluation of XiTAO Software Topologies

#### 4.1.1.1. Methodology

This section describes the experimental methodology used to evaluate the contributions of of the XiTAO topologies presented in D3.3. LAGRES is integrated into XiTAO<sup>1</sup>, a DAG runtime system implemented on top of C++11. XiTAO is designed to flexibly evaluate scheduling policies and already features moldable tasks, i.e., those that can be mapped to a single or multiple threads. This facilities the mapping of N (coarsened tasks) to M (elastic resources) [24]. However, LAGRES is decoupled from the runtime implementation.

# Platforms:

Experiments are performed on three architectures: AMD Abu Dhabi, Intel Broadwell and Intel Haswell with the structure described in Table 4.1. The AMD Abu Dhabi machine has 4 AMD Opteron processors (6348), each having 2 chips, with 6 cores each, for a total of 48 cores. The

<sup>&</sup>lt;sup>1</sup>https://github.com/mpericas/xitao.git

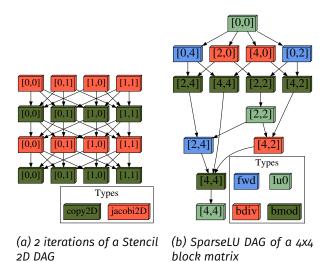

Figure 4.1. Sample dependency graphs for the analyzed applications.

other two machines belong to academic research computing centers. One node on each machine is used exclusively (i.e. with no other jobs co-scheduled on the node during the experiments). The nodes of the Intel Haswell cluster have 2 Xeon E5-2650v3 processors, with 10 cores each, for a total of 20 cores. Also, we use a "large memory" Intel Broadwell cluster, where each node contains 4x18 Xeon E7-8860v4 cores, for a total of 72 cores.

### **Baseline Schedulers:**

In the following, we describe and justify the baseline schedulers used.

**Random Work-Stealing Scheduler (RWSS)**: it is based on distributed work-stealing, where each worker greedily tries to reduce idleness by fetching work from victim queues. It has been formally introduced in [8] and has appeared in several parallel task-based libraries such as Cilk [7], MassiveThreads [21] and Intel TBB [17].

**Locality-Aware Work-Stealing Scheduler (LAWS)**: this scheduler is introduced in [11]. It is helpful in this evaluation as it is an incremental improvement over RWSS. Also, it provides work-stealing within the NUMA node of task's initialization, and tries to optimize cache misses within the node. Using ideas from LAWS, we allow work-stealing within the inclusive partitions set where the task has been initialized, and we greedily fill in the resource partitions to construct cache-friendly subtrees of the DAG.

**Locality-AGnostic Scheduler (LAGS)**: we also evaluate the proposed scheduler without the effect of moldability. Partition widths are persistently set to 1. Tasks are initialized and executed in the NUMA node mapped by their STA. Local stealing is preferred, then global stealing requests are fulfilled when the stealing thread reaches idleness threshold and the steal that reduces the cost function (as per the model) is chosen.

LAGRES: the adaptive locality scheduler based on XiTAO topologies introduced in D3.3.

# Applications:

**Iterative DAG - HEAT:** we leverage a DAG implementation to compute heat diffusion on a 2D grid. One of the iterative numerical methods to achieve this is to use 2D Jacobi stencil [15]. We use a 5-point stencil and create dependencies between the neighbor nodes (see Figure 4.1a). The approach involves computing the stencil in a compute task, and copying out the update in a copy task. The DAG is iteratively executed for a predefined number of iterations. For STA specification, we use the coordinates of block of mesh points involved in a task.

**Recursive DAG - SparseLU:** we port a SparseLU benchmark from the Barcelona OpenMP Tasks

(b) Intel - Broadwell

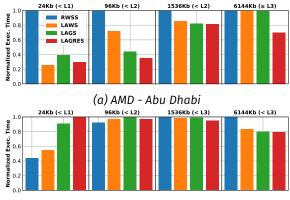

Figure 4.2. SparseLU parallel execution time on 8x6-core AMD - Abu Dhabi and 4x18-core Intel Broadwell as you increase the task input size in bytes. Matrix size = 128 x 128 blocks.

Suite [14]. This benchmark computes an LU matrix factorization over sparse matrices. The matrix is composed of NxN blocks, each of which has a pointer to a sub-matrix of size MxM. Load-imbalance is evident due to the sparsity of the matrix. For each phase of the LU algorithm, a task is spawned for non-empty blocks (see Figure 4.1b). For STA specification, the matrix block indices are used.

#### 4.1.1.2. Evaluation

In this section, we share the obtained empirical results comparing LAGRES to the baseline schedulers. Then, we analyze the achieved performance gains by showing the schedule map for LAGRES pertaining to a specific task type and location, and how locality is preserved adaptively. Also, we explain the gains by relating them to the proportion of the cumulative work time to the overall scheduling time.

#### **Empirical Results:**

Figure 4.2 depicts the SparseLU normalized (to max) execution time of the evaluated schedulers factorizing a double-precision 512x512 matrix, block dimension size of 32, 64, 256 and 512, respectively. The block sizes are varied to span different cache-levels in the system . The experiments are run on 48 threads (AMD Abu Dhabi) and 72 threads - (Intel Broadwell). The layout description corresponds to the sharing levels of the underlying architecture, and the sharing is enabled to the socket level. In Figure 4.2a, we use 1, 2, 6, 12, which maps to L2, L3 and socket-level sharing. With the exception of the smallest case (< L1), it is noted that the proposed scheduler in both its variants (LAGS and LAGRES) performs better than the baselines. Enabling elasticity provides a considerable improvement when L3 cache size is exceeded. According to our data, the adaptive socket level sharing provides higher streaming bandwidth due to interleaving over 2 NUMA nodes for the tasks that benefit from this (one with low arithmetic intensity), otherwise, the reduction in idle-time due to lower cost of molding to larger widths in the cases of tasks with higher arithmetic intensity. LAGS has an almost similar behavior to LAWS, as the model does not help much in improving over LAWS when resources are not properly utilized with moldability. The Intel Broadwell exhibits less cache/memory access heterogeneity due to less sharing. This limits the analysis of LAGRES to a few partitions, and yields to local/global work-stealing scheduler. Hence, the performance is bounded by LAWS with the exception of the larger cases when streaming provides an advantage. Note that the slight improvements seen for task sizes of (1536Kb and 6144Kb) are factors of 10s and 100s of seconds.

Figure 4.3. Time to solution for different mesh sizes to compute 5-point stencil on two architectures. Iteration count = 2000

Figure 4.4. Comparison of the cumulative work/other distribution, and the scheduling trace for a Stencil (compute and copy) tasks. The denoted tasks have a single software topology address. Mesh resolution =  $2048 \times 2048$ .

It is also important to stress test LAGRES by conducting a scalability analysis to assess whether checking the model incurs an overhead that hinders performance gains. Figure 4.3 shows the execution time of the stencil application comparing the different schedulers as the resolution of the mesh is increased (resulting in more smaller tasks). The case of  $1024 \times 1024$  yields around 128x128 mesh points per tasks after decomposition. In essence, this is too fine grain not to observe a degradation compared to LAGS and LAWS due to the slight overhead that can diminish the benefits for smaller-sized tasks. This is also in line with the results obtained in SparseLU (Figure 4.2). The effect of resource elasticity contributed by LAGRES becomes especially clear as the problem size is increased across the 2 architectures. In the case of AMD Abu Dhabi depicted by Figure 4.3a, we observe improvements of at least 30% over LAWS and RWSS in the  $2048 \times 2048$  case. The behavior is sustained on Intel Haswell shown by Figure 4.3b.

#### Analysis:

One of the important attributes to be analyzed in task-based runtime scheduling is the proportion of work-time, that is time spent executing the tasks, to other scheduling activity, which includes queue management, scheduling logic, dependency checks, idleness, etc. In Figure 4.4a, we show the cumulative work time, that is the thread total time x the number of threads vs. the total other time on Intel Haswell for the stencil application  $2048 \times 2048$ . The reduction in time-to-solution incurred by LAGRES mostly manifests as reduction in work time. According to our profiling data, the adaptation to locality constrains by LAWS explains the increase of "other" time. To see LAGRES in action, we display the scheduling trace for the compute and copy tasks

of the stencil. We pick a sequence of tasks dependencies that are initialized on the nodes highlighted by the Figures 4.4b and 4.4c. To reduce clutter, we omit the selected resource width and just show the leader thread for the selected resource partition. For the compute task executed on AMD Abu Dhabi, we can see that in some instances, LAGRES still chooses to schedule away from the data location, which appears to be an effective technique that reflects in reduction of time-to-solution even though data locality is not strictly preserved. However, this is not the case in the stencil copy task, where streaming bandwidth, and reduction of cache latency are crucial to achieve higher throughput. Hence, LAGRES is able to discover these attributes (i.e. the computational requirements) adaptively and without prior assumption about the nature of the workload.

### 4.1.2. The XiTAO heterogeneous scheduler

# 4.1.2.1. Energy Efficient Task Scheduler

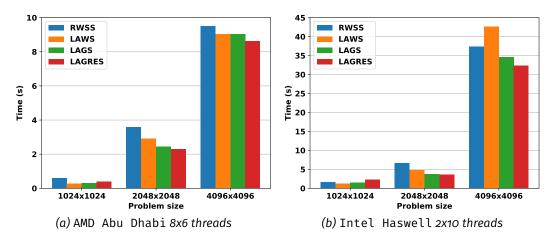

Based on the proposal of energy efficient task scheduler runtime in D3.3, we conduct more real applications evaluation of energy savings on two different platforms. The details of platforms and applications are introduced as following:

**Asymmetric platform.** NVIDIA Jetson TX2 features a dual-core NVIDIA Denver 2 64-bit CPU and a quad-core ARM A57 Complex (each with 2 MB L2 cache). The board is set to MAX-N nvpmodel mode. The Denver and the A57 cores implement the ARMv8 64-bit instruction set and are cache coherent. The two clusters, i.e. Denver and A57, support the same range of frequencies and the platform only allows cluster-level frequency changes. Note that the A57 cluster cannot be powered off.

**Symmetric platform.** It features a dual-socket 10-core Intel 2650v3 (code-named "Haswell") node and runs Linux version 3.10.0. RAPL is used to build the power profiles and measure the energy consumption on the platform.

**Image Classification (Darknet-VGG-16 CNN)** is a 16-layered deep neural network. It is implemented as a fork-join DAG that spans all the layers. Each task of the DAG performs GEneral Matrix Multiplication (GEMM) operations on a sub-partition. No task criticality assignment exists in VGG-16 since all the tasks within a layer have the same properties and dependencies.

**Heat Diffusion** is implemented on a 2D grid by using one of the iterative numerical methods: 2D Jacobi stencil. It involves computing the stencil as compute-bound tasks, and copying out the update as memory-bound tasks. The DAG is iteratively executed for a predefined number of iterations (1000 in this work). The resolution is set to 10240 and the external DAG is constructed via slab (1D) decomposition into four domains. We also experiment with other decompositions, such as pencil (2D), without change in conclusions. The Heat DAG is symmetrical, thus no task criticality assignment is performed.

**Sparse LU Factorization** is selected from the Barcelona OpenMP Tasks Suite. This benchmark computes an LU matrix factorization over sparse matrices. The matrix is composed of N×N blocks, each of which has a pointer to a sub-matrix of size M×M. The application includes four kernels: LUO, FWD, BDIV and BMOD. Among of them, LUO, FWD, BDIV are set as critical tasks.

**Evaluated Scheduling Policies.** In order to evaluate proposed energy efficient task scheduling techniques, we utilize random work-stealing (abbr. RWS) as a baseline scheduler. RWS is a typical and widely used scheduling scheme for task-DAGs, which still works well in asymmetric environment. It is a greedy scheduler that tries to keep all cores busy. This results in more tasks

#### Table 4.2. Summary of evaluated runtime strategies

| Name                                        | Acronym      | Notion                                                                   |

|---------------------------------------------|--------------|--------------------------------------------------------------------------|

| Random Work Stealing (with Sleep)           | RWS (+Sleep) | Typical greedy scheduling (enhanced with "Sleep")                        |

| Fastest Cores with Criticality (with Sleep) | FCC (+Sleep) | Performance-oriented criticality task scheduling (enhanced with "Sleep"  |

| Lowest Costs with Criticality (with Sleep)  | LCC (+Sleep) | Lowest cost-oriented criticality task scheduling (enhanced with "Sleep") |

| Lowest Energy without Criticality           | LENC         | The goal of scheduling each task targets lowest energy                   |

| Lowest Energy with Criticality              | LEC          | The goal of scheduling critical tasks targets performance                |

Figure 4.5. Energy comparison of three synthetic benchmarks on Intel Haswell.

being scheduled to powerful cores, which achieves execution time balancing between asymmetric cores. Each task is executed on a single core in the RWS baseline.

In addition, we compare with a performance-oriented criticality aware scheduler (abbr. FCC). FCC is inspired by related work criticality aware task scheduler CATS [13], but instead of using one core for each task in CATS, FCC features task moldability, i.e. each task can be executed on multiple cores, which could show the benefit of task moldability by comparing to RWS. In comparison to RWS, FCC has criticality awareness and critical tasks in FCC are dynamically scheduled to the fastest configuration pair (leader core, resource width) by globally checking all possible configurations in the dynamic performance modeling table described in D3.3, while non-critical tasks only search locally for the fastest resource width (i.e. task moldability) without changing the launching core. We also develop a lowest cost-oriented criticality aware scheduler (abbr. LCC). The difference between FCC and LCC is that LCC attempts to minimize the parallel costs, i.e. the product: execution time  $\times$  the resource width. We also enhance these three schedulers with the same exponential backoff sleep strategy to study this energy conservation technique.

The energy efficient scheduler (LENC) is a variant that steers all tasks for the lowest energy, independent of task criticalities. Finally, to learn the impact of critical tasks on energy efficiency, we devise a lowest energy with criticality scheduler (LEC) which assigns critical tasks to the fastest configuration pair, similar to FCC. All evaluated schedulers and their variants are described in Table 4.2.

#### 4.1.2.2. Evaluation Results

Figure 4.5 shows energy consumption of different scheduling policies when running three synthetic benchmarks with different DAG parallelisms ranging from 2 to 16. Note that we evaluate a wider DAG parallelism spectrum (i.e. we include p=16) since the symmetric platform comprises more cores. The results show that LENC consumes less energy than other scheduling policies and the energy reduction is significant especially when DAG parallelism is low. In the case of MatMul with low DAG parallelism, RWS only utilizes a single core for executing a task, while under-utilized cores consistently attempt work stealing resulting in a considerable increase in

Figure 4.6. Energy comparison results of three applications on two platforms. MAX & MIN in x-axis of Figure 4.6a means that on TX2 Denver cluster's frequency is maximum and A57 cluster's frequency is minimum.

energy consumption. On the contrary, LENC is able to achieve high energy efficiency through moldable execution of tasks. Wider width selection aids in effectively reducing the energy consumption by limiting periods of under-utilization. With FCC, 95.5% tasks execute with a resource width of 10 since it is the fastest configuration and 1.6% execute with a resource width of 5. In comparison, LENC executes 96.1% tasks with a resource width of 10 and 3% tasks with a resource width of 5, which further reduces under-utilization. The gap between LENC and FCC reduces with increasing DAG parallelism since there is a decline in the under-utilization period.

In this section, we analyze the impact of the scheduling features using three real applications. VGG-16 is an inference workload that is typical of mobile and edge devices. We use the Nvidia TX2 platform as it features characteristics typical from this domain (asymmetry, low core counts). The Heat and Sparse LU benchmarks are common HPC workloads that we evaluate on the dualsocket Intel multicore node (symmetric, high core count). We also evaluated the opposite configurations which leads to the same conclusions and is not further discussed here.

**Asymmetric Platform.** Figure 4.6a shows energy consumption when running VGG-16 application on TX2. The results show that the LENC scheduler is the most energy efficient scheduler across different frequency settings. This scheduler achieves 31% to 75% energy reduction in comparison to RWS, and from 19% to 68% energy reduction compared to FCC and between 25% to 73% energy reduction compared to LCC. This can be attributed to the benefits by using task-type aware execution and task moldability of LENC when running on asymmetric platforms.

**Symmetric Platform.** In order to show the genericity and portability of our proposal, we also evaluate two applications i.e. Heat and Sparse LU, on one symmetric platform Intel Haswell. Figure 4.6b and 4.6c show the energy consumption comparison between different scheduling strategies. The results show again that LENC achieves better results than other scheduling policies. To understand the effectiveness of LENC, we analyze the resource width distribution across different scheduling policies for Heat. The result is shown in Figure 4.7. The figure shows that the majority of tasks in FCC execute with a resource width of 10. In contrast, in the case of LCC 70% of tasks execute with a resource width of 1 due to reduced parallel cost associated with the execution. In the case of LENC, the number of tasks that execute with a resource width of 5 and 10 are almost equal. This happens because in Heat there are two different types of kernels with different scalability: *jacobi* and *copy*. The *jacobi* kernel is compute-bound and while *copy* is memory-bound. LENC is able to determine an optimal width for each kernel. During the run, 98% of *jacobi* tasks execute with a resource width of 10 as it the most energy efficient configuration while 97% of the *copy* tasks execute with a resource width of 5.

Figure 4.7. Heat task distribution with different resource width on Intel Haswell.

Figure 4.8. Overview of Pipelined CNN in XiTAO.

# 4.1.3. Support for Pipeline Parallelism

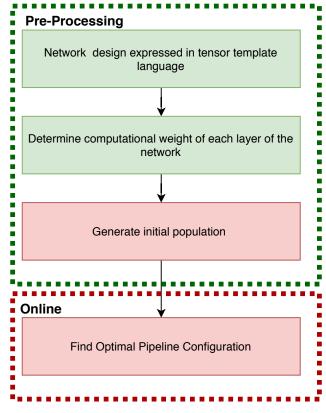

XiTAO now supports pipeline parallel execution of Convolutions neural networks. The system overview is depicted in figure 4.8. The Framework consists of 2 modules.

- In Pre-processing module, We determine the computational hints from network descriptor. The hints provide a notion of computational weights of each layer based on which we model the initial partition of network layers to generate a pipeline stage.

- 2. In the online module, we measure the configurations which are highly expected to be a good candidate for a balanced pipeline on a given platform. The training finishes when algorithm has found the optimal solution for mapping. Rest of the input data is then processed in pipelined fashion.

# 4.1.4. Pipelined execution of VGG-16

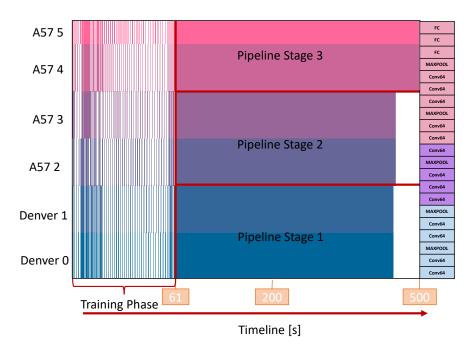

The figure 4.9 shows two phases of execution:

Figure 4.9. Execution timeline of VGG 16 on Nvidia Jetson TX2.

- 1. The training phase of the execution.

- 2. The normal phase of the pipeline processing.

During the training, after 61 input frames, the algorithm converged to a 3-Staged pipeline. The core partitioning is static and pre-decided for each pipeline stage count. Pipeline Stage 1 comprises of first 6 layers and executes on 2 Denver cores. Pipeline Stage 2 comprises of next 5 layers and executes on 2 A57 cores. Pipeline Stage 3 comprises of the last 10 layers and executes on 2 A57 cores.

As throughput maximizing pipeline is the one which has smallest bubble size and the slowest stage takes minimum possible time. The bubble size is referred to as the latency gap between the execution time of pipeline stages, zero bubble size ideally means a fully balanced pipeline. Thus the configuration is chosen based on the fact that it minimizes the bottleneck of the pipeline. As we can also observe in the figure 4.9, the resulting pipeline has a negligibly small bubble size.

# 4.2. OmpSs

# 4.2.1. OmpSs@FPGA, OpenCL and CUDA

In this section we show the evaluation of the OmpSs support for Intel FPGAs (including environments with FPGAs and Nvidia GPUs), the evaluation of OmpSs@FPGA on Xilinx FPGAs, using the ZCU102 development kit, and the development and evaluation of the OmpSs-2 support for Xilinx FPGAs.

# 4.2.1.1. OmpSs support for CUDA and OpenCL

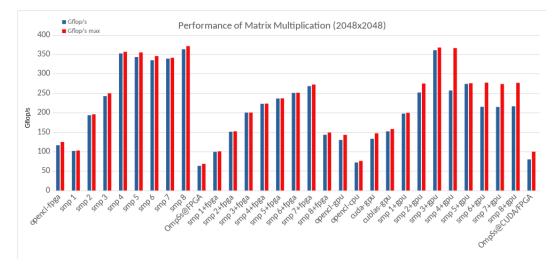

We have evaluated the OmpSs support for OpenCL FPGAs and Nvidia GPUs, with two different environments:

• Intel Arria 10 FPGA: single chip 4 core Intel Core(TM) i7-6700 @ 4GHz, with hyperthreading, Terasic de5net a7 Arria 10 FPGA, and Nvidia GeForce GTX Titan X GPU. Matrix multiplication

is executed with a matrix size of 2048x2048 single precision values, and a block size of 64x64 elements.

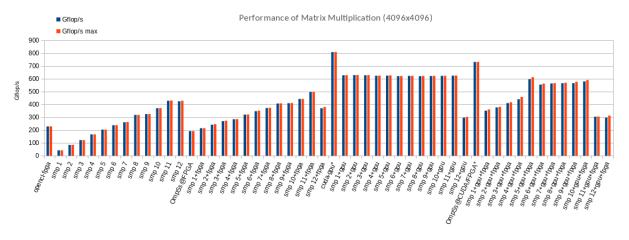

• Intel Stratix 10 FPGA: dual chip 6 core Intel Xeon(R) Bronze 3204 @ 1.9GHz, without hyperthreading, Intel Stratix 10 FPGA, and Nvidia GeForce RTX 2070 SUPER GPU. Matrix multiplication is executed with a matrix size of 4096x4096 single precision values, and a block size of 128x128 elements.

Figure 4.10 shows the performance obtained on the Matrix Multiplication benchmark using the combined OmpSs@OpenCL, to execute work on the Arria 10 FPGA, and OmpSs@CUDA, to execute work on the Nvidia GeForce Titan X GPU. The benchmark uses the implements approach to indicate that the block by block matrix multiplication kernel on block sizes of 64x64 elements is available in three versions: for the Intel cores, using the MKL library, for the Arria 10 FPGA, compiled from OpenCL, and for the Nvidia GPU provide in CUDA or using the CUBLAS library.

Results show that OmpSs running on the FPGA only (labeled OmpSs@FPGA) introduces some overhead compared to the native OpenCL execution (1st column, labeled opencl-fpga).

In this particular case, the FPGA performance is comparable to the performance of a single Core i7 (labeled smp 1). The SMP cores scale up to 4, reaching around 350 Gflop/s. Hyperthreads (labels smp 5 to smp 8) do not add additional performance due to the sharing of the floating point units across them. This is a well-known behaviour for hyperthreading and HPC applications.

Nevertheless, hyperthreading is actually providing additional performance when used in combination with the FPGA. In this case, every core included in the execution, adds 50 Gflop/s (labels smp 1+fpga to smp 4+fpga) and every additional hyperthread adds around 20 Gflop/s (smp 5+fpga to smp 7+fpga). The particular case of smp 8+fpga gets lower performance as in this case we need to have one of the hyperthreads running matrix multiplication kernels in the SMP, and also taking care of the events of the FPGA through the OpenCL runtime. This sharing is introducing delays in the synchronization and this lowers the performance obtained.

The performance is compared also with the CUDA versions (labeled cuda-gpu and cublas-gpu). They obtain around 150 Gflops, and when adding additional cores (labels smp 1+gpu to smp 3+gpu) we achieve an increase in performance. When using 4 additional cores, the performance is getting a lot of variability due to the use of one additional hyperthread to manage the GPU. This seems to indicate that the management of the GPU takes more resources than the management of the OpenCL FPGA, if we compare columns smp4+gpu with smp 4+fpga.

Hyperthreading is not helping in any of the cases, labels smp 5+gpu to smp 8+gpu. Finally, label OmpSs@CUDA/FPGA shows the performance obtained when using the CUDA GPU and the OpenCL FPGA at the same time. In this case, we do not use additional SMP cores, as they only reduce the performance obtained. As there is no device that outperforms the rest, in this case the data transfers between the GPU/FPGA and main memory hinder the possibility to obtain performance when using both devices.

Figure 4.11 shows the performance obtained when running the same benchmark on the Stratix 10 FPGA and GeForce RTX 2070 SUPER GPU.

Comparing the performance of OmpSs with the FPGA (labeled OmpSs@FPGA), with the performance of the native OpenCL execution, we also observe a light drop in performance due to the overhead of OmpSs task management.

Figure 4.10. Performance of OmpSs@OpenCL/CUDA Matrix Multiplication on the Intel Arria 10 FPGA and the Nvidia GeForce GTX Titan X GPU

In this case, the SMP cores (with no hypertreading), labels smp 1 to smp 12, scale from around 40 Gflop/s to 420 Gflop/s when using 11 cores. The single core performance is much lower than the Intel Core i7, but the Xeon architecture provides better memory bandwidth, and scalability. This also allows that 11 cores add performance on top of the FPGA (labels smp 1+fpga to smp 12+fpga). The later smp 12+fgpa is not scaling properly due to the sharing of one core between the SMP tasks execution and the FPGA management.

On this environment, the Nvidia GPU is much more powerful that the rest of the devices (label cuda-gpu, reaching 800 Gflop/s). This prevents getting additional performance when adding cores to the experiments (label smp 1+gpu to smp 12+gpu). In these cases, the GPU is so fast that allowing a core getting a task for execution already slows down the execution of the benchmark.

When using the combined execution on GPU and FPGA, the performance is also reduced compared to GPU only, as the effect is similar. The task executing on the FPGA delays the rest of the application. On this environment, we also show how the cores contribute when using the GPU and the FPGA. Initially the performance drops a lot (smp 1+gpu+fpga), increasing slightly with additional cores (smp 2+gpu+fpga to smp 5+gpu+fpga), and getting a little lower and stable up to smp 10+gpu+fpga. The executions on smp 11+gpu+fpga and smp 12+gpu+fpga get lower performance due to the overhead introduced by sharing two cores with SMP execution and GPU and FPGA management.

In conclusion, we think that the implements approach can be interesting when the performance of the several resources used is not so different, like what happens with the FPGA and the SMP cores, and in those situations adding several additional cores to the execution can improve the performance (like in the experiments labeled smp 1+fpga to smp 11+fpga).

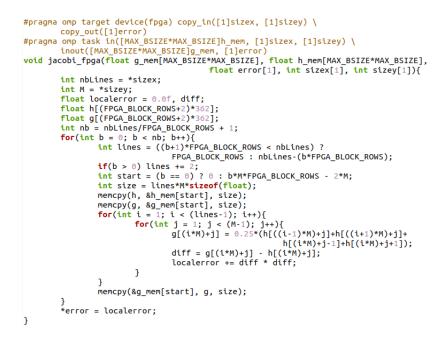

# 4.2.1.2. OmpSs@FPGA energy efficiency

We have executed a set of matrix multiplication experiments in the Xilinx ZCU102 development kit, with 4 ARM A53 cores and an integrated XCZU9EG FPGA. Each matrix multiplication experiment consists of 20 executions of matrix multiply, on a matrix of 2816x2816 single precision floating point elements. The matrix is blocked in tiles of 256x256 values.

The program uses OmpSs to offload tasks, either to the FPGA or the ARM cores. The FPGA is programmed through OmpSs to have 3 instances of the matrix multiplication IP core, that can

Figure 4.11. Performance of OmpSs@OpenCL/CUDA Matrix Multiplication on the Intel Stratix 10 FPGA and the Nvidia GeForce RTX 2070 SUPER GPU

be used in parallel, and independently of each other.

Figure 4.12 shows the power consumption of the execution of 7 experiments, in this order:

- 1. the two first peaks reaching up to 18W (between seconds 17-33 and 49-65, are two executions of the 20 matrix multiplications, using the 3 instances of the matrix multiplication IP core.

- 2. the next two peaks reaching 14W (between seconds 75-97 and 110-129) are two executions of the 20 matrix multiplications, using 2 of the IP core instances.

- 3. the next two sets of bars reaching 10.5 11W (seconds 141-200 approximately) are the same two executions of the 20 matrix multiplications, using a single of the IP core instances.

- 4. the final flat line stable at 3W is the same execution of the 20 matrix multiplications using the 4 ARM A53 cores only. In this last execution, we have substracted the power consumption of the PL logic (around 3.8W while idle), as it is not used in the execution.

Figure 4.12 shows the total power consumption (light blue line), the Processing System (PS) power (dark blue), and the Processing Logic (PL) power (yellow), as the main contributors. DDR, BRAM, and Management power consumptions are constantly below 0.5W.

If we compute the GFlops obtained by the different sets of executions, we get:

- 3x IP core instances achieve 94.5 Gflops, with a mean consumption of 15.1W and a maximum of 6.26 GFlops/W.

- 2x IP core instances achieve 77.6 Gflops, with a mean consumption of 10.6W and 7.32 GFlops/W. This is the best energy-efficient experiment.

- 1 IP core instance achieves 47.1 Gflops, with a mean consumption of 9.2W and 5.11 GFlops/W.

- 4 ARM A53 cores achieve 12.1 Gflops, with a mean consumption of 2.95W, and 4.1 GFlops/W.

Performance (GFlops) and energy efficiency (GFlops/W) for the same experiments is shown in Figure 4.13. Results show that the best performance is obtained with 3 matrix multiply IP accelerators, while the best energy efficiency is obtained with 2 matrix multiply IP accelerators.

Figure 4.12. Online power consumption on the matmul experiments with OmpSs@FPGA

Figure 4.13. Performance and energy-efficiency with OmpSs@FPGA matrix multiplication

Concluding, the code transformations done with OmpSs to exploit matrix multiplication on the FPGA result in an increase of the GFlops/W obtained from the Zynq U+ chip, increasing power efficiency when using more resources in the FPGA fabric.

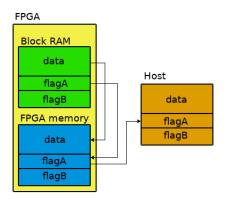

# 4.2.1.3. OmpSs-2 support for FPGA/CUDA separate memories

While developing the new OmpSs-2 runtime system, we have had the need to incorporate support for GPUs and FPGAs with separate global memory. This environment covers discrete GPUs with or without unified memory support and discrete FPGAs. We have designed the directory and software caching mechanism for OmpSs-2 to support such devices. This work has been done in the context of a master thesis [28]. From the compiler, at task creation point the nanos6 runtime receives the information on the task dependences, that can be directly used to implement the data caching mechanism on the target device memory, and issue the memory transfers. Those memory transfers are implemented by means of the CUDA runtime, for Nvidia GPUs, and using our xtasks/xdma [9] libraries for Xilinx FPGAs. We have leveraged the same code generation that we use for OmpSs-1 in OmpSs-2, so the infrastructure that we have in the FPGA is the same, and it changes the software side that we have made integrated with the OmpSs-2 runtime system.

Figure 4.14 shows the comparison of the performance obtained on the matrix multiplication benchmark on the ZCU102 FPGA environment, when using different matrix sizes and the OmpSs-1 and OmpSs-2 environments. As it can be seen the performance is very similar, with a small performance drop on the new OmpSs-2 environment, that we will examine and try to further reduce in the future. Figure 4.15 shows the comparison of the performance obtained in the OmpSs-2 environment, with the new OmpSs-2 directory/cache support, OmpSs-2 with Prefetching and OmpSs-2 with Unified Memory. Results demonstrate that the new implementation of OmpSs-2 with the directory/cache outperforms both the prefetching and the unified memory support. This fact makes us think that the implementation done with the directory and cache

support will be useful for future developments with OmpSs-2.

Figure 4.14. Comparison of the performance of OmpSs-1 and OmpSs-2 matrix multiplication on the ZCU102 FPGA development kit, with the new OmpSs-2 directory/cache support

Figure 4.15. Comparison of the performance of OmpSs-2 matrix multiplication, with the new OmpSs-2 directory/cache support, OmpSs-2 with Prefetching and OmpSs-2 with Unified Memory

# 4.2.2. OmpSs@Cluster

OmpSs-2@cluster is the distributed memory variant of the OmpSs-2 programming model. It is based on the latest iteration of the OmpSs programming model, *i.e.*, OmpSs-2 [5], which supports efficient task nesting through weak dependencies and early release of dependencies [23]. OmpSs-2@cluster was originally developed in ExaNoDe [27], and it is compatible with the SMP version of OmpSs-2, so that the same program and compiled binary can be executed on either an SMP or a cluster of SMPs. OmpSs@cluster has been part of the OmpSs-2 public release since June 2019.

# 4.2.3. Smart-Mirror/OmpSs@Cluster

The Smart Mirror use case is an interactive human interface to a smart environment, such as a home, where sensory information is collected from the surroundings to give the user helpful information, such as the weather forecast or temperature, in addition to helping them by monitoring, remotely controlling or automating their daily actions (*e.g.*, opening a window or setting a schedule) [30].

The Smart-Mirror software comprises an object recognition module that employs a neural network to identify objects and faces seen by the mirror, in addition to voice and gesture con-

trol modules. The hardware prototype and setup employs two NVIDIA Jetson Xavier developer boards.

The object detection module includes a camera part by which an image is captured (in raw format) from a video stream and processed (*e.g.*, scaled) to match the requirements of the neural network that performs the actual object detection and extraction. Finally, a Kalman and Hungarian filter step is introduced which increases the certainties of current detection by incorporating previously detected objects along with the new ones.

OmpSs-2@cluster allows the CPU and GPU compute to be divided among two nodes, increasing the frame rate by a factor of three from 6 fps to 19 fps at a 17% increase in power consumption, from 47 W to 55 W. This is possible using the annotations described in this section at minimal development cost.

# 4.2.3.1. Single Node Implementation

The original implementation run on a single Xavier board, leaving the second node non-utilized. The single node implementation also executed the camera, neural network, and Kalman filter parts sequentially, hence not fully utilizing all the cores on the single Xavier node.

Figure 4.16 highlights a snippet code of the original implementation. The neural network is initialized (line 2) according to some desired configurations and weights. The application goes into the main loop (line 11), which runs until the program quits. At each iteration, it captures an image (line 14) from the camera, feeds this image to the network (lines 18–19), and finally applies the Kalman filter (line 23).

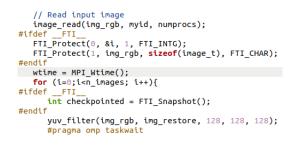

#### 4.2.3.2. OmpSs-2@Cluster Implementation

The main objective was to divide the work between the two Xavier nodes such that the first node will be used for the camera capturing part alongside other modules, while the second node accelerates the object detection and the filter parts. It was also necessary to do so in a portable and productive way, including the minimum of details about the platform and no explicit data transfers. To fully utilize both Xavier nodes, the Smart-Mirror application (specifically the object detection, and the camera parts) was ported to OmpSs-2@Cluster task-based programming model, and executed by the Nanos6 runtime system that implements the OmpSs-2@Cluster model.

Porting Smart-Mirror to OmpSs-2@Cluster required a straightforward and clear transformation by dividing the code into tasks. The *taskification* was done by surrounding the single node code with directives (#pragmas). To express data dependencies between different tasks, extra clauses in, out, and inout were appended to the #pragmas to specify all memory accesses of these data. Tasks are then executed in parallel by the Nanos6 runtime, and easily scheduled by the runtime to run on any desired Xavier node. Scheduling tasks to run on a specific node however can be forced by using the node clause.

Figure 4.17 and Figure 4.18 shows the OmpSs-2@Cluster taskified code for the same code in Figure 4.16. Task init\_node\_one represents the neural network initialization. As mentioned above, since the prediction step will be entirely computed on the second Xavier node, we use the node clause here with value of 1 indicating that we want to schedule this task on the second node (counting from 0). The node clause was introduced in D3.3 [25].

As mentioned earlier, at each iteration we capture an image frame, perform predictions, then

```

// Initialize the neural network with the given weights

1

2

network = load_network_custom(CFG_FILE, WEIGHT_FILE,1,1);

set_batch_network(network, 1);

3

4

fuse_conv_batchnorm(*network);

calculate_binary_weights(*network);

5

6

. . .

// Initialize Kalman and Hungarian filter

8

init_trackers(classes)

9

. . .

// Main loop

11

While(1)

{

13

// Capture raw image from the camera and scale it.

14

inS = get_image_from_stream_resize(cap, IMAGE_WIDTH, IMAGE_HEIGHT,

CHANNELS, &pInImg, 1);

16

. . .

17

// Feed the image into the netwrok and perform prediction.

18

network_predict_image(net, det_s);

19

pDetections = get_network_boxes(network, IMAGE_WIDTH, IMAGE_HEIGHT,

THRESH, HIER_THRESH, 0, 1, &nBoxes, 0);

21

// Update the tracked detections using the Kalaman filter.

23

updateTrackers(*pDetections, nBoxesTaskThreshed, THRESH, &pTrackedDets,

24

&trackedNBoxes, IMAGE_WIDTH, IMAGE_HEIGHT);

25

}

```

Figure 4.16. Single node implementation of the object detection part of the smart mirror.

```

1

#pragma oss task out(nBoxesLastLoop, pTrackerIDLastLoop, pObjectTypLastLoop,

\

2

pBBoxLastLoop, pDets0, pDets1, nBoxesTask0, nBoxesTask1,

١

3

pNetwork, pIn1S1,pIn0S1) in(classes) node(1) label("init_node_one")

4

{

5

. . .

6

pNetwork = load_network_custom(CFG_FILE, WEIGHT_FILE, 1, 1);

set_batch_network(pNetwork, 1);

8

fuse_conv_batchnorm(*pNetwork);

9

calculate_binary_weights(*pNetwork);

init_trackers(classes);

11

. . .

}

```

# Figure 4.17. Initialization step of the OmpSs-2@Cluster implementation of of the object detection part of the smart mirror.

update the tracked features (trackers) resulted from the predictions using the Kalman filter. Since the image frame capturing code is executed entirely on the first node and also it will be the only code that will be executed on the first node, so it is not taskified and is executed as a normal function call, get\_image\_from\_stream\_resize. Note that the captured image on node 1 needs to be copied to node 2 for the predictions, however OmpSs-2@Cluster simplifies this by only adding a pointer to the image data as an input dependency to the predict task,

```

1

While(1)

2

{

if(itr % 2 == 0) //even iteration

4

{

inS0 = get_image_from_stream_resize(cap, IMAGE_WIDTH, IMAGE_HEIGHT, CHANNELS,

5

6

&pInImg, 1);

. . .

8

#pragma oss task in(pData1[0; inSDataLength]) node(1) label("even_buffer")

{

for (size_t i = 0; i < inSDataLength; ++i)</pre>

pIn1S1->data[i] = pData1[i];

}

. . .

#pragma oss task in(pIn0S1) node(1) label("even_predict")

{

. . .

17

network_predict_image(pNetwok, *pIn0S1);

*pDets0 = get_network_boxes(pNetwok, IMAGE_WIDTH, IMAGE_HEIGHT, THRESH,

HIER_THRESH, 0, 1, nBoxesTask0, 0);

. . .

}

. . .

#pragma oss task out(nBoxes) out(pBBox[0;4*defaultDetectionsCount]) \

out(pTrackerID[0;defaultDetectionsCount])

\

out(pObjectTyp[0;defaultDetectionsCount])

١

out(changed) node(1) label("even_update")

{

. . . .

updateTrackers(*pDets1, *nBoxesTask1, THRESH, &pTrackedDets, &trackedNBoxes,

IMAGE_WIDTH, IMAGE_HEIGHT);

. . .

}

} else // odd iteration

{

// same as the even iteration, howver using pData0 buffer

}

```

hence data copy will be made implicitly by the Nanos6 runtime.

To add more parallelism, we needed to execute the prediction step concurrently with the update step. However the update cannot occur until after the prediction has been made. Hence we use two predictions buffers pDets0, and pDets1, iteration (i+1) will be predicting the current iteration (i) image frame, and updating the the predictions of the previous iteration (i-1). To avoid copying the data between the two buffers at each iteration, we divide the while loop into even and odd iterations, and swap the pointer passed to each of the prediction, and update tasks.

Note that the node(1) clause is also used with the even\_buffer, even\_predict, and even\_update tasks to schedule them on the second Xavier node as desired. In addition, transferring the image is implied via the dependency representation clause.

|                        | Single        | Node          | OmpSs-2@Cluster |               |  |  |  |

|------------------------|---------------|---------------|-----------------|---------------|--|--|--|

|                        | Xavier node 1 | Xavier node 2 | Xavier node 1   | Xavier node 2 |  |  |  |

| <b>CPU utilization</b> | 30%           | 0%            | 116%            | 122%          |  |  |  |

| <b>GPU utilization</b> | 80%           | 0%            | 0%              | 80%           |  |  |  |

Table 4.3. CPU and GPU utilization of the single node and the OmpSs-2@Cluster implementations running alone.

|                        | Frame rate | Power consumption |

|------------------------|------------|-------------------|

| Single node            | 6 fps      | 47 W              |

| OmpSs@cluster two node | 19 fps     | 55 W              |

Table 4.4. Frame rate and power consumption of whole smart mirror application.

#### 4.2.3.3. Results

To fully utilizing both Xavier nodes and shifting the GPU usage from the first Xavier node entirely to the second Xavier node, Table 4.3 shows the CPU and GPU utilization of the single node implementation versus the OmpSs-2@Cluster.