# D4.4 "REPORT ON ENERGY-EFFICIENCY EVALUATIONS AND OPTIMIZATIONS FOR ENERGY-EFFICIENT, SECURE, RESILIENT TASK-BASED PROGRAMMING MODEL AND COMPILER EXTENSIONS"

Version 2

# **Document Information**

| Contract Number      | 780681                                                                                                                                                                                                                                                                                                   |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project Website      | https://legato-project.eu/                                                                                                                                                                                                                                                                               |

| Contractual Deadline | 30 November 2020                                                                                                                                                                                                                                                                                         |

| Dissemination Level  | Public                                                                                                                                                                                                                                                                                                   |

| Nature               | Report                                                                                                                                                                                                                                                                                                   |

| Author               | Marcelo Pasin (UNINE)                                                                                                                                                                                                                                                                                    |

| Contributors         | Isabelly Rocha (UNINE), Christian Göttel (UNINE), Valerio<br>Schiavoni (UNINE), Pascal Felber (UNINE), Gabriel Fernandez<br>(TUD), Xavier Martorell (BSC), Leonardo Bautista-Gomez (BSC),<br>Mustafa Abduljabbar (CHALMERS), Oron Port (TECHNION),<br>Tobias Becker (MAXELER), Alexander Cramb (MAXELER) |

| Reviewers            | Madhavan Manivannan (CHALMERS), Daniel Ödman (MIS),<br>Elaheh Malekzadeh (MIS), Chistian von Schultz (MIS), Hans<br>Salomonsson (MIS)                                                                                                                                                                    |

The LEGaTO project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement No 780681.

# Change Log

| Version | Description of Change                                       |

|---------|-------------------------------------------------------------|

| 1503    | 2020-10-01, File created, Initial draft structure           |

| 1513    | 2020-10-02, Added energy-efficient IoT draft                |

| 1547    | 2020-10-27, Added secure service networking in OP-TEE       |

| 1552    | 2020-10-27, Added Fault Tolerance introduction              |

| 1560    | 2020-10-28, Added refs to secure service networking         |

| 1564    | 2020-10-28, Added trusted consensus                         |

| 1579    | 2020-10-29, Added smart contract execution in ARM TrustZone |

| 1580    | 2020-10-29, Added enhanced XiTAO data parallel interface    |

| 1585    | 2020-10-29, Applied corrections to security section         |

| 1586    | 2020-10-29, Included first structure of DFiant evaluation   |

| 1587    | 2020-10-29, Added Initial IDE description                   |

| 1588    | 2020-10-29, Added initial version of dfiant integration     |

| 1592    | 2020-11-01, Added Pipetune                                  |

| 1597    | 2020-11-02, Applied small corrections, reordered sections   |

| 1611    | 2020-11-03, Edited improvements in DFiant section           |

| 1700    | 2020-11-13, Added Mercurium                                 |

| 1711    | 2020-11-16, Added Alya                                      |

| 1712    | 2020-11-16, Added reference to D3.4 for OmpSs@cluster       |

| 1713    | 2020-11-16, Added Eclipse Che, updated references           |

| 1718    | 2020-11-16, Added task graph analysis                       |

| 1726    | 2020-11-17, Added SGX/OmpSs integration                     |

| 1759    | 2020-11-22, Document restructuration, introduction written  |

| 1766    | 2020-11-25, Completed IDE plugin and SGX results            |

| 1822    | 2020-11-26, Completed summary and conclusion                |

| 1836    | 2020-12-01, Applied reviews                                 |

| 2018    | 2021-02-02, Created second version, fixed references        |

| 2039    | 2021-02-04, Provided main findings in executive summary     |

| 2048    | 2021-02-05, Applied reviewer suggestions                    |

This log reflects actual revision numbers from SVN (version control software used).

# Index

| 1 | Exec                      | utive Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Intro                     | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 | 3.1                       | piler support and Development Environment11Task graph analysis113.1.1Project goals113.1.2Useful acceleration information113.1.3Acquiring program traces133.1.4Testing193.1.5Limitations and future work22Enhanced XiTAO Data Parallel Interface233.2.1The Asynchronous Data Parallel Mode243.2.2The Synchronous Data Parallel Mode253.2.3Evaluation of the Alya solver25OmpSs Integration with SGX27IDE Plugin313.4.1Eclipse plugins313.4.3Working with OmpSs in Eclipse Che333.4.4Conan-based installations33 |

| 4 | <b>Data</b><br>4.1<br>4.2 | flow engines36DFiant Evaluation364.1.1Programmability364.1.2Performance and Other Metrics38Integration with OmpSs38                                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | 5.1                       | gy-Efficiency39Energy-efficient IoT Applications395.1.1Networking in ARM TrustZone405.1.2Executing Smart Contracts in ARM TrustZone425.1.3Achievements44Energy Efficiency Through Deep Learning Parameter Tuning445.2.1Problem statement455.2.2Implementation465.2.3Evaluation46                                                                                                                                                                                                                               |

| 6 | <b>Secu</b><br>6.1<br>6.2 | rity and Fault-Tolerance52Trusted Consensus in Untrusted Environments526.1.1Architecture526.1.2Overview526.1.3Results54FPGA Fault Tolerance57                                                                                                                                                                                                                                                                                                                                                                  |

| 7 | Conc                      | lusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8 | Refe                      | rences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# List of Figures

| 3.1        | Tiled n-body program graph for a trivial problem size.                              |          |

|------------|-------------------------------------------------------------------------------------|----------|

| 3.2        | Tiled n-body graph at a larger (though still trivial) problem size                  | 12       |

| 3.3        | A set of tasks suitable for collective acceleration.                                | 13       |

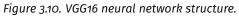

| 3.4        | A loopflow graph for the VGG16 CNN.                                                 | 14       |

| 3.5        | Diagram of Mercurium analysis infrastructure.                                       |          |

| 3.6        | Diagram of main loop detection process.                                             |          |

| 3.7        | Illustration of vertex merging.                                                     | 18       |

| 3.8        | Task assignment fitness function.                                                   | 18       |

| 3.9        | Analyzed task graph; 32768 bodies, 512x512 tiles, 4 iterations                      |          |

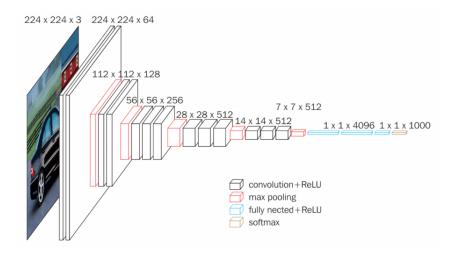

| 3.10       | VGG16 neural network structure.                                                     | 21       |

| 3.11       | VGG16 loop flow graph after analysis.                                               | 21       |

| 3.12       | Analyzed task graph, choleksy decomposition, 2048x2048 matrix with tile size 256x25 |          |

| 3.13       | The basic structure of a DAG based program inserting SPMD code regions              |          |

| 3.14       | XiTAO data parallel modes                                                           |          |

| 3.15       | The basic structure of a DAG based program inserting SPMD code regions              |          |

|            | Intel SGX applications with OmpSs support.                                          |          |

| 3.17       | Evaluation results for Cholesky Kernel application.                                 |          |

|            | Evaluation results for Dot Product application.                                     | 20<br>29 |

|            | Evaluation results for matrix multiplication application.                           |          |

|            | Evaluation results for STREAM application (barrier based version).                  |          |

|            |                                                                                     |          |

|            | Evaluation results for STREAM application (dependency based version).               |          |

|            | IDE plugin showing the OmpSs dependences hints offered to the programmer            |          |

|            | IDE plugin showing the OpenMP task hints offered to the programmer                  |          |

|            | Workspace selection in Eclipse Che with OmpSs@FPGA available                        |          |

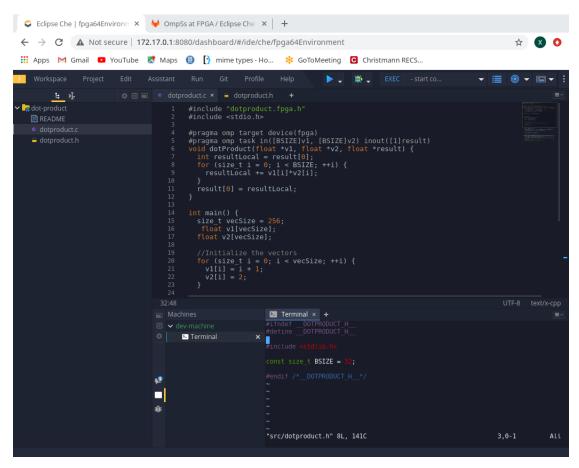

| 3.25       | Dotproduct project in OmpSs@FPGA open with Eclipse Che                              | 34       |

| 4.1        | Example of a script in DFiant that runs simulation in GHDL                          | 37       |

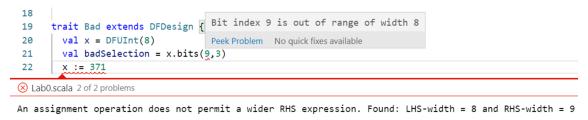

| 4.1<br>4.2 | Example of DFiant bit-accurate compile-time error indications in the editor         |          |

|            | ALU manual pipelining example and running compiled code inspection                  |          |

| 4.3        | ALU inspected code printout. Notice the addition of balancing pipe stage.           |          |

| 4.4        | ALO Inspected code printout. Notice the addition of balancing pipe stage            | 30       |

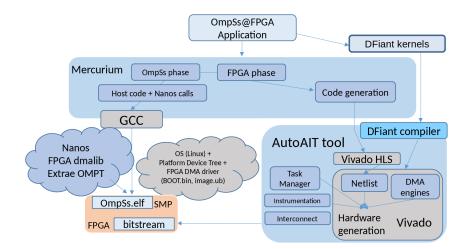

| 4.5        | Compilation environment showing the integration of the DFiant kernels onto the      |          |

|            | OmpSs toolchain                                                                     | 40       |

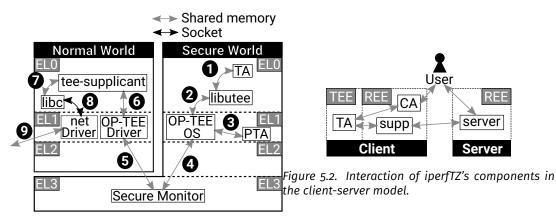

| 5.1        | Execution flow inside OP-TEE                                                        | 41       |

| 5.2        | Interaction of iperfTZ's components in the client-server model                      | 41       |

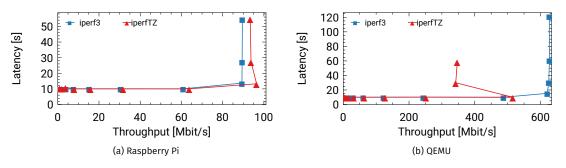

| 5.3        | TCP network throughput measurements for 128 KiB buffer sizes.                       |          |

| 5.4        | Energy consumption during TCP network throughput measurements. Bit rates on         | 44       |

| 5.4        | the x-axis are given in logarithm to base 2.                                        | 1.2      |

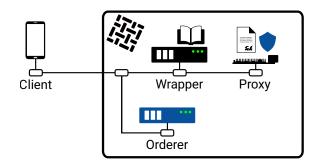

| 5.5        | Architecture of TZ4FABRIC                                                           | 42<br>42 |

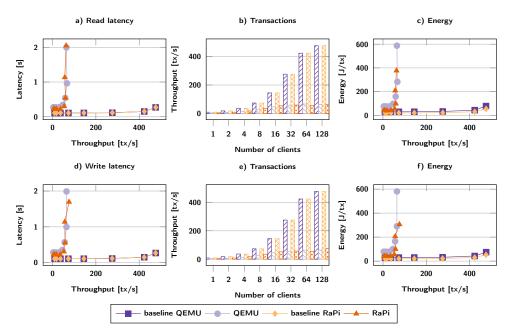

| 5.6        | Throughput-latency, transactions and transaction energy for read/write invoca-      | 42       |

| 5.0        | tions. Top row are read transactions, bottom row are write transactions             | 12       |

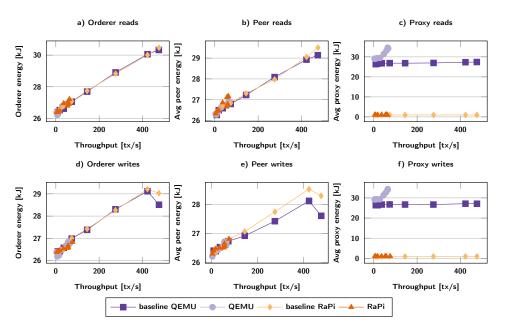

|            | Energy consumption of nodes in the Hyperledger Fabric network. Top row are read     | 43       |

| 5.7        |                                                                                     | .,       |

| - 0        | transactions, bottom row are write transactions.                                    | 44       |

| 5.8        | Hyperparameter tuning flow.                                                         | 45       |

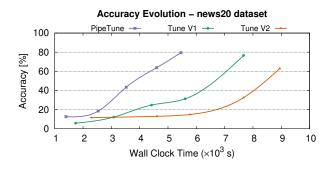

| 5.9        | Accuracy convergence.                                                               | 47       |

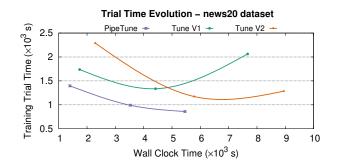

| 5.10       | Training trial time convergence.                                                    | 48       |

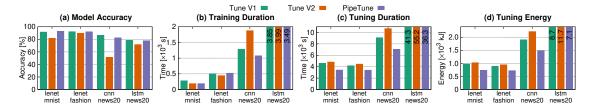

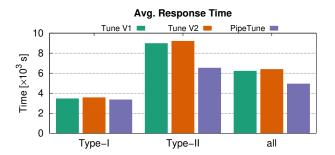

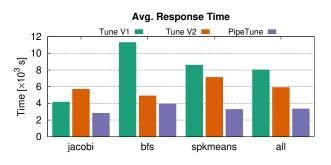

| 5.11       | Evaluation of PipeTune's accuracy, performance and energy consumption for Type-     |          |

|            | I and Type-II Jobs.                                                                 | 48       |

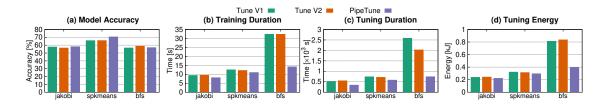

| 5.12       | Evaluation of PipeTune's accuracy, performance and energy consumption for Type-     |          |

|            | III Jobs                                                                            | 48       |

|     | Average response time for Type-I and Type-II Jobs considered independently and<br>all together.Average response time for Type-III Jobs. |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

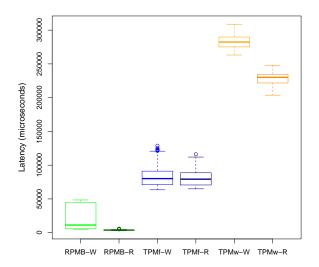

| 6.1 | RPMB x fresh and worn out TPM NVRAM monotonic counter - Latency distribution for reads and writes                                       | 55 |

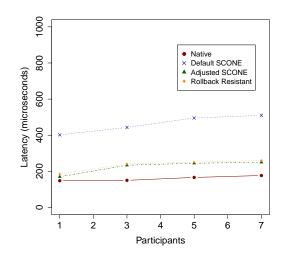

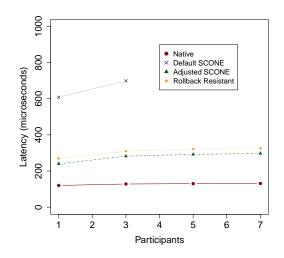

| 6.2 | Trusted Replication Latency - retrieve performance for large queries                                                                    |    |

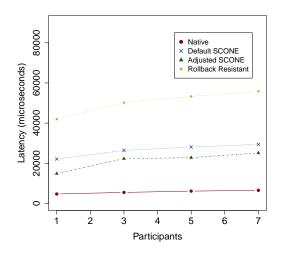

| 6.3 | Trusted Replication Latency - update performance for large queries                                                                      | 57 |

| 6.4 | Trusted Replication Latency - Insertion performance                                                                                     | 57 |

# List of Tables

| 3.2<br>3.3 | Summary of task cost evaluation methods                                                                                      | 19<br>25 |

|------------|------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1        | Comparing various RTL codes with equivalent DFiant codes in LoCs The DFiant im-<br>plementation is usually much more concise | 39       |

| 5.1        | Workloads used for experiments                                                                                               | 46       |

# **1. Executive Summary**

This report is the final and last delivery of the work produced in LEGaTO's Work Package 4, regarding the toolchain frontend. As it was in all previous cases, it is issued at the same time as Deliverable D3.4 on the backend, and includes many components that complement the ones presented there. This deliverable historically complements previous deliverables SD1 (Chapter 4), D4.2 and D4.3. To avoid overlap between this and previous documents, we choose to highlight only those components that are novel or have been considerably updated since D4.3. Overall, this deliverable covers work that has been done during the past 6 months, from M30 until M36. The text of this deliverable reports the status of the LEGaTO tool chain frontend (work package 4) and is organized in four main technical chapters.

**Chapter 3** Compiler Support and Development Environment

**Chapter 4** Integration of the Dataflow Programming Substrates

Chapter 5 Energy-Efficiency

Chapter 6 Fault-Tolerance and Security

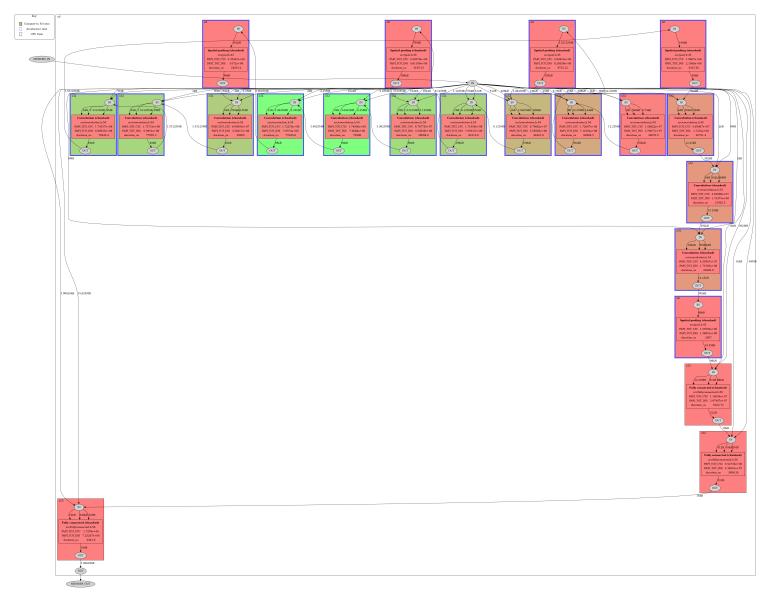

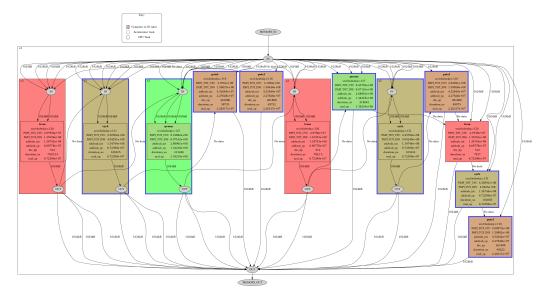

Chapter 3 starts with Section 3.1, which provides information about the work done on the compiler front-end as well as the programming environment. Its first section presents the task graph analysis developed when considering the integration of Maxeler's MaxCompiler into LEGaTO's stack. We describe how we brought together the Maxeler MaxCompiler and OmpSs, having OmpSs' task-based programming model to assist the dataflow development process, reducing efforts to develop and to optimise dataflow accelerators for the Maxeler platform. We have implemented a tool to automatically detect static sub-graphs from applications annotated in OmpSs, and show them to the programmer to easily identify parts of the algorithm that should be mapped to Maxeler's DFE accelerator. We demostrate that it is possible in many cases to analyse and reduce large task graphs, getting useful insights into program structure.

Section 3.2 presents the work done on enhancing XiTAO's data parallel interface, explaining how it distinguishes synchronous and asynchronous modes of execution. We enhance the XiTAO data-parallel interface to support both synchronous and asynchronous modes of operation, exposing XiTAO features of LEGaTO's tool-chain backend, via loop-parallelism. Due to its popularity in fork-join parallel programming models, the synchronous data-parallel interface provides energy-efficient execution enabled by dynamic moldability and task-based power profiling (demonstrated in D3.4) for a wide range of applications, especially those the adopt kernels from the Machine Learning and Numerical Science fields. We were able to demonstrate the energy efficiency of the enhanced version using a C++ port of the Alya code (from the Smart City use case). There, we compare to a highly optimized work-stealing scheduler and achieve more than 50% better energy-efficiency while still achieving faster time-to-solution on the heterogeneous Nvidia TX2 CPU architecture.

A performance evaluation of OmpSs when running tasks inside SGX enclaves appears in Section 3.3. We have achieved secure task execution within an OmpSs application, by means of using Intel SGX Enclaves as the secure framework. The Enclave interface is very similar to the OmpSs task interface, so mapping tasks onto it is straightforward. With this platform, we have been able to measure the performance penalty that the secure infrastructure introduces to secure the data, with and without encryption, and we have observed that a good way to overcome this penalty is by using task-level parallelism.

Section 3.4 concludes Chapter 3, presenting the last evolution of the Integrated Development Environment. As presented in previous deliverables, we developed a set of Eclipse IDE Plugins with the goal to provide programming hints to the user. The add-on provides context-based help regarding the OmpSs/OpenMP directives and clauses, assisting on the decision about what is the most appropriate expression for the heterogenous parallelism. We have also achieved the integration of the OmpSs development environment as a Docker container within Eclipse CHE.

Our work regarding dataflow engines appears in Chapter 4, which in this deliverable is entirely dedicated to present our work with DFiant, the dataflow hardware description language that decouples functionality from implementation developed in LEGaTO. Our main contribution focuses on the DFiant evaluation and the significant improvements in programmability of FPGA devices without sacrificing performance or fine-grain hardware generation control. Our empirical findings show that DFiant designs usually save between 50% to 70% in lines of code compared to the RTL baseline.

Chapter 5 highlights the progress done in energy-efficiency, in two sections. All research results described in this chapter were published and presented as peer-reviewed papers in conferences.

We present a study of IoT applications running in trusted environments, with special attention given to power consumption when using Arm's TrustZone in Section 5.1. We developed two tools, a network perfomance evaluation tool for secure services, and an extension of Hyperledger Fabric for running (blockchain) smart contracts, both using OP-TEE and exploiting ARM TrustZone. The performance tool is capable of identifying bottlenecks in the network performance of secure services, for which we were able to identify and quantify the energy and performance overheads. Using the smart contract tool, we have shown that it is possible on ARM hardware to reduce the energy cost by one order of magnitude compared to state-of-the-art hardware used with Hyperledger Fabric. The improved energy consumption comes at the cost of performance, which is also a result of the additional security when running the service in OP-TEE or ARM TrustZone in general.

Section 5.2 is dedicated to a study of adapting system- and hyperparameters in machine learning jobs in order to be be more energy-efficient. We designed and implemented a novel parameter tuning algorithm for deep learning clusters which takes system parameters into account. Our work resulted in an open-source tool that leverages the repetitive behaviour of tuning jobs for deep neural networks, to quickly find the best set of parameters. The tool is modular which makes it easy to swap between similarity functions and underlying search algorithms. We evaluated 7 different real-world datasets from different domains, including text classification and image recognition. When compared against state-of-the-art deep neural network tuning systems, our tool shows evidence that we can greatly reduce tuning and training time (27% and 41% respectively) without accuracy loss.

The final technical part is Chapter 6, with two sections. Section 6.1 contains a thorough study on how to implement trusted consensus using SGX enclaves, including an evaluation with a replicated database. Trusted consensus is a rollback-resistant, integrity preserving data service that aims to provide data replication in untrusted cloud environments. It combines hardware enforced anti-rollback mechanisms over a customized protocol that executes database requests and replicates the changes. To address attacks that involve abusing the protocol majority balance, we use a single-instance protocol that leverages hardware monotonic counters to ensure that attacks are much harder to achieve. Our results demonstrated that the associated overheads are limited and scale harmoniously.

Section 6.2 concludes our last technical chapter, with a brief reference of LEGaTO's Fault Tolerant Interface to use with FPGAs, as it has been previously described in Deliverable D4.3. Also, in Deliverable D5.3 we presented the work of Alya at large scale, a LEGaTO use case in a smart city simulation that sometimes runs for long hours on the Marenostrum supercomputer in Barcelona. To mitigate the high probability of failures during Alya jobs, we apply checkpoint/restart as described in Deliverable D3.3, substantially decreasing the amount of re-computation required upon a failure. We created a tool capable of checkpointing heterogeneous applications running on CPU and GPU clusters. Our tool uses multiple storage systems to implement multilevel checkpointing with parallel device-to-host data streams when writing into reliable storage. With FTI, we have enabled fault tolerance for heterogeneous applications while substantially decreasing the checkpoint and recovery time. Our work around FTI and Alya was also published and presented as a peer-reviewed paper in a conference.

# 2. Introduction

LEGaTO is a Horizon 2020 research and innovation action to develop advanced techniques to make it easier to build large performance-hungry applications. This deliverable marks the end of the work done in LEGaTO's Work Package WP4, named "Tool-chain front-end". WP4 was composed of seven tasks, each task producing research outputs on a different aspect being developed in WP4. The tasks are listed below.

- Task 4.1: Definition / Design (M1-9)

- Task 4.2: Programming Model features for energy efficiency (M1-36)

- Task 4.3: IDE plugin (M7-36)

- Task 4.4: Compiler support (M7-30)

- Task 4.5: High-level Synthesis for FPGA (M1-36)

- Task 4.6: Task-based kernel identification/DFE mapping (M7-36)

- Task 4.7: Fault Tolerance and Security (M1-36)

WP4 was intended to develop techniques for high-productivity, energy-efficient, high-performance heterogeneous programming with added security and fault-tolerance. Heterogeneity is obtained using computers that incorporate central processing units (CPUs), field-programmable gate arrays (FPGAs), and graphics processing units (GPUs). Security is obtained by using novel hardware extensions that allow for building trusted execution environments. Fault-tolerance is managed using standard techniques, tailored for the original environment developed in the project.

Requirements for the techniques developed in WP4 (energy efficiency, security, fault-tolerance, performace) may compete against each other, so we often strived for finding adequate tradeoffs. To achieve application development under such constraints, a great number of components has been developed, allowing to map applications written in a high-level task-based dataflow language onto the heterogeneous platform. Each component presents different ways of tackling different requirements, working at different levels, and often obtaining trade-offs between two or more aspects. Finally, the components in WP4 are developed in tight integration with the work done in WP3. Many times, deliverables from WP3 refer to work done in WP4, and vice-versa. In the paragraphs that follow, we recap the deliverable history of WP4, then we present the structure for this document.

**Deliverable D4.1** (Definition/design of front-end toolbox) was integrated in Chapter 4 of Superdeliverable SD1 [34]. It corresponded to the work done in Task 4.1 (Definition/Design), ended at month 9. SD1 contains a comprehensive set of functionalities designed to be offered as frontend tools for programming applications. A software architecture was introduced with all main aspects on which LEGaTO is focused, along with a number of extensions, then proposed to be implemented in the infrastructure management to support the execution of the proposed task model.

**Deliverable D4.2** (First release of energy-efficient, secure, resilient task-based programming model and compiler extensions) was delivered at month 20. It presented OmpSs, the execution and programming model for the tool chain, with a description of the resource sharing between different runtimes. For programmability, we proposed the development of OpenMP and OmpSs support into Eclipse and we developed our first plugins. We extended the OmpSs compiler to support autoVivado, to compile OmpSs applications which target Xilinx FPGAs. We also developed and assessed a checkpoint-restart fault-toloerant library to be integrated inside the runtime system. We analysed energy-efficiency and security trade-offs, with different trusted hardware support, and produced the design of a task-based scheduler called HEATS. To understand the overhead generated by trusted execution environments, we also developed a monitoring framework. Finally, we designed and started implementing DFiant, a Scala-embedded hardware description language that leverages dataflow semantics to decouple functionality from implementation constraints.

**Deliverable D4.3** (Final release of energy-efficient, secure, resilient task-based programming model and compiler extensions, including FPGA toolchain) was delivered at month 30. There, we presented our work to upgrade OmpSs to support FPGAs, including autoAIT (to support Xilinx ZCU102) and Vivado HLS 2019.3. We offered a DAG-friendly data-parallel interface for XiTAO runtime system, leveraging its energy-efficient scheduling features on heterogeneous platforms. We also added a Maxeler DFE architecture plugin to the OmpSs runtime, to support spawning of tasks to Maxeler hardware. We extended the compiler to obtain the communication weights and computation load, helping to decide the proper mapping of DFE kernels. Our first experiments using OmpSs with SGX are also presented, with new tools for monitoring and for adding fault-tolerance to legacy applications inside SGX enclaves. The IDE plug-in also evolved, to support addition, a simplified finite state machine syntax and constraint tags for injecting RTL-like semantics, along with is first OmpSs integration. We proposed a novel data deduplication technique that allows for saving energy of IOT devices. Finally, we have rewritten the core of the smart city use case to use our checkpointing library.

This is **Deliverable D4.4**, the last deliverable of Work Package WP4. Here, we detail the research progress we made in the last few months of LEGaTO concerning front-end tools for productivity, security, fault-tolerance and energy efficiency. Mimicking previous deliverables, D4.4 contains four technical chapters. Each of these chapters is presented below.

Chapter 3 (compiler support and development environment) is split into four sections. In Section 3.1 we present how we automatically identify static sub-graphs in OmpSs' task graph for mapping them to Maxeler's dataflow engines and we demonstrate it with three different algorithms: n-body simulation, a neural network, and Cholesky matrix decomposition. We describe the enhancements provided on top of the XiTAO data parallel interface in Section 3.2. With this interface, applications can leverage the XiTAO runtime for energy efficiency and interference awareness, and resource moldability. The section concludes with an evaluation of the Alya solver with different programming models including OpenMP, OmpSs, and XiTAO. Section 3.3 describes our efforts on integrating secure tasks into OmpSs using SGX and, finally, Section 3.4 presents the last improvements made with the IDE plugin.

Chapter 4 contains two sections concerning DFiant dataflow engines. Section 4.1 presents an evaluation of DFiant, focusing on programmability of FPGA devices. Section 4.2 shows how DFiant kernels are integrated with OmpSs in a FPGA project.

Chapter 5 presents two recent research results on energy efficiency. Section 5.1 presents an analysis of the energy-efficiency of two distributed, hardware-secured services specifically designed for IoT devices. Section 5.2 presents a novel study about how to tune machine learning models' hyperparameters in order to trade performance for energy efficiency.

Chapter 6 is the last chapter, containing our last months' contributions on security and faulttolerance. Section 6.1 presents recent research results on hardware-secure computing with an implementation of a distributed consensus algorithm in an untrusted environment. Section 6.2 contains a summary of the progress of fault-tolerant checkpointing for FPGAs, and refers to the work reported in D4.3 (of Work Package WP3).

# 3. Compiler support and Development Environment

## 3.1. Task graph analysis

Here we consider integration of the Maxeler MaxCompiler into the LEGaTO tool stack. As described in deliverable D2.1, Maxeler uses a dataflow oriented model to describe accelerators for FPGA-based Dataflow Engines (DFE), and the compiler uses a Java-based meta-language MaxJ to describe the compute kernels. Since developing and optimising a dataflow accelerator in MaxJ can involve a considerable amount of effort, we want to leverage the task-based programming model in OmpSs to assist the dataflow development process. The task-graph generated by OmpSs is conceptually very suitable for being translated into a dataflow model. Therefore, we want to automatically identify static sub-graphs in the task graph generated from OmpSs and translate them into a form that helps the developer to identify parts of the algorithm that should be mapped to the DFE accelerator. This includes analysis of the compute to I/O ratio of the subgraphs to be accelerated.

The process for developing an accelerator for any given program begins with an understanding of the algorithm to be accelerated. The next step is the identification of compute intensive portions of code, then finally the transfer of those code sections to the accelerator. This can be a straightforward process when the implementation is well understood, however in real world scenarios it is often the task of a developer to optimize an existing implementation for which complete information is not available.

#### 3.1.1. Project goals

The goal of the task graph analysis project is to investigate automated analysis of task-based program traces. The aim being to aid developers by providing the insight they need to make good acceleration decisions for existing applications. This step of gaining insight into the program is crucial, especially for FPGAs because of high implementation effort and large time requirements for generating FPGA bitstreams.

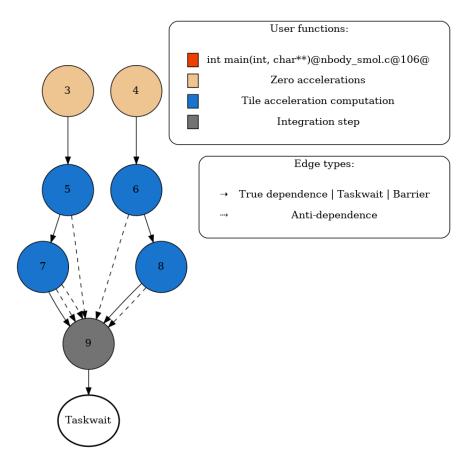

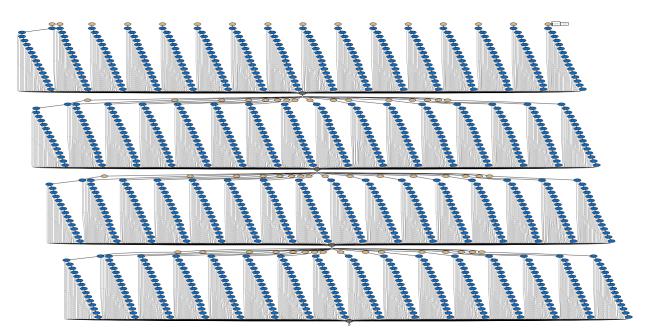

For trivial examples, tools like graphviz can easily render visual representations of task graphs as in Figure 3.1. For programs at realistic problem sizes though, these graphs quickly become unintelligible as in Figure 3.2.

## 3.1.2. Useful acceleration information

One important metric for accelerating code is the ratio between task cost and the size of the working set. Typically the best candidates for acceleration are pieces of code that involve large amounts of processing and small volumes of data. To determine these quantities, the task cost in terms of primitive operations as well as the size of task inputs and outputs need to be instrumented and made available for processing. In the case of FPGA accelerators it is also important to know the types of operations taking place in tasks, as the hardware cost of implementation can vary significantly between operation types.

In a task graph, nodes represent tasks and edges represent dependencies between tasks due to shared variables or other synchronization. It is important to capture this structural information in the analysis as it is possible for a collection of tasks to represent a better candidate for acceleration than any individual task. Figure 3.3 contains a graph with several tasks, none of which are ideal acceleration candidates by themselves. Collectively however, they make a better candidate for acceleration than any individual task.

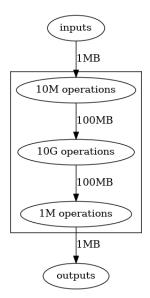

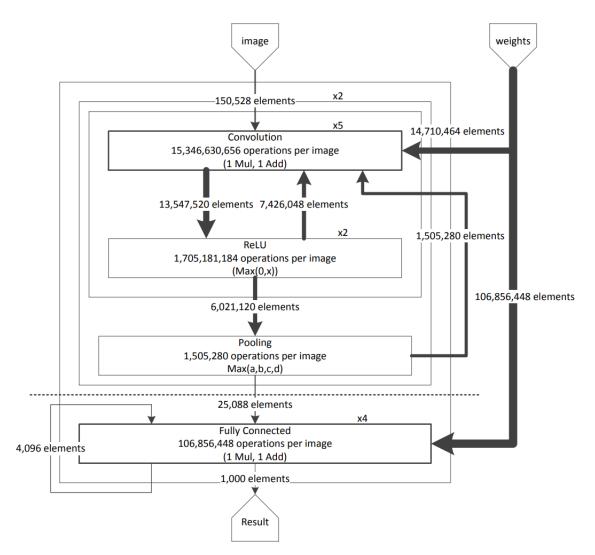

Collected information needs to be displayed to the user in a meaningful way. One representation that suits this purpose is the loop-flow graph (see Figure 3.4). A Loop-flow graph is a form of task graph where iterative processes are folded away to hide redundant information. Nodes in the graph represent operations within the code and are optionally annotated with an iteration count to indicate that the process runs multiple times. Edges are annotated with the quantity of data moving between tasks. The graph may be partitioned to indicate which tasks take place on the accelerator and which take place on the CPU. In the case of the graph in Figure 3.4, tasks above the dotted line (convolution, rectifier linear operator and spatial pooling steps) are on

Figure 3.1. Tiled n-body program graph for a trivial problem size.

Figure 3.2. Tiled n-body graph at a larger (though still trivial) problem size.

the accelerator, whereas the fully connected layers are on the CPU. This assignment of tasks was determined by manual analysis.

Figure 3.3. A set of tasks suitable for collective acceleration.

#### 3.1.3. Acquiring program traces

Data exfiltration was achieved using the instrumentation capabilities of the nanox runtime. The nanox instrumentation API was expanded to include events for task I/O ranges and operation counts and a new instrumentation plugin was implemented to export this data in a machine readable format for further processing.

#### 3.1.3.1. Mercurium analysis infrastructure

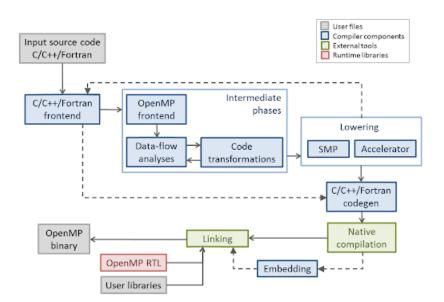

To facilitate the evaluation of task cost and enumeration of operations, a pass was implemented using the Mercurium analysis infrastructure to compute expressions for the number of operations in each task. Mercurium is a source-to-source compiler for C/C++ and FORTRAN with support for parallel programming models like OpenMP and OmpSs. It is formed by a series of phases that analyze and transform the code, which is later passed to a native compiler to generate the final binary. The picture in Figure 3.5 shows a high level overview of the compiler pipeline.

Mercurium implements a series of phases devoted to source code analysis, particularly of Open-MP/OmpSs codes. The infrastructure is built on top of a Parallel Control Flow Graph (PCFG) that represents the flow of the source code as well as the parallelism and other semantics expressed by OpenMP/OmpSs directives. Based on this representation, Mercurium offers different classical data-flow analysis, including use-definition chains and reaching definitions, and optimizations, like constant propagation and strength reduction, all adapted to consider the parallel semantics of OpenMP/OmpSs. Finally, more complex analysis like induction variables analysis and scalar evolution are available.

#### 3.1.3.2. Estimating task cost

With the objective of estimating the cost of relevant regions of code, a set of features have been included in the Mercurium compiler. These are the following:

- A new analysis phase that computes the cost of OmpSs tasks and loops in terms of number of operations. The operations are organized based on the type of the operands (i.e., integer, float or double) and the type of the operation (i.e., addition/subtraction, multiplication or division), resulting in a total of 9 groups.

- A new transformation phase that instruments the user code with the information of the counters computed by the analysis. This code is executed at runtime generating per region events containing the operation counts.

Figure 3.4. A loopflow graph for the VGG16 CNN.

Figure 3.5. Diagram of Mercurium analysis infrastructure.

The new analysis phase performs a top-down inside-out traversal of the user code using the PCFG. This means that, although the code is traversed sequentially, inner levels are computed before outer levels, e.g., in a two-level nested loop, the counters of the inner loop are computed first, and then aggregated accordingly to the values of the variables of the outer loop. The main computations occur in the following points:

- Loops: the number of operations of the region inside the loop is multiplied by the number of iterations of the loop. In case the number of iterations depends on another induction variable, then this computation is delayed until the different values of the outer induction variable are known.

- Conditional statements: unless the condition of the statement can be decided to be true or false, the number of operations of each branch is computed, and then just the maximum of the two is used as an approximation.

- Tasks: the number of operations of the task region is computed.

- Function calls: when the code of the function code is accessible, the compiler performs inter-procedural analysis; otherwise, the function is also annotated as a different type of operation, so the number of times this function is called can also be computed.

The analysis does not modify the user code in any way. However, the information gathered about the counters is stored in the PCFG structure, particularly in the nodes corresponding to loops and tasks, for later use. Furthermore, the results are also detailed in a report available to the user.

The new transformation phase provided in Mercurium uses the data included in the PCFG during the analysis phase to instrument the user code using the API provided by Nanos to that end. The instrumentation occurs in two different places:

- The code associated with the task constructs include a new event at the end with the expression that computes the number of operations of each type.

- Loops include instrumentation before and after the loop, so the region associated with the counter can be recognized at runtime. In this case, if the compiler has not been able to compute the number of iterations, instrumentation is added to compute it at run-time (unlike for tasks, this cannot be automatically done at run-time because loops are not recognized by the Nanos runtime systems as tasks are.

In addition to the Mercurium analysis pass, two other methods for assessing task complexity were also implemented. One uses execution duration of the task as an approximation for task cost, and another uses processor hardware counters via the PAPI library to estimate operation counts. Support and accuracy for these methods varies and is summarised in Table 3.1.

#### 3.1.3.3. Acquiring data ranges

The nanox runtime supports several different models for task dependencies as separate plugins that can be activated at runtime. To capture memory ranges associated with dependencies, the cregions (contiguous regions) plugin was used. To determine the data size of a given dependency, start addresses and end addresses were compared to determine the total size of the data.

#### 3.1.3.4. Task graph analysis

Gathered data is processed using a set of analysis tools. These tools are responsible for processing the graph and delivering data to the user in a readable format. Before discussing the analysis process in detail it is important to define some terminology:

| Method                     | Support                                                                    | Accuracy                                                                                                                                                        |

|----------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Execution time             | High - Always available.                                                   | Low - Many variables not accounted<br>for (CPU cache, processor perfor-<br>mance, compiler optimisations). No<br>way to distinguish between operation<br>types. |

| Hardware counters          | Medium - Counter sup-<br>port varies between pro-<br>cessors.              | Medium - Variances due to compiler<br>optimisation and non-task code being<br>counted. Some operation types can be<br>distinguished.                            |

| Mercurium analysis<br>pass | Low - Difficult to achieve<br>robust operation for arbi-<br>trary programs | High - Results are invariant between<br>runs and accurately represent opera-<br>tions as expressed in the source code.                                          |

Table 3.1. Summary of task cost evaluation methods.

- Task instance: Refers to an instance of a task. There may be many instances of any given task on a graph.

- Task: Refers to the source code associated with a task instance.

- Vertex: Vertices on a task graph represent task instances. For the purposes of this section, the term can be considered synonymous with the term "task instance".

- Dependence: An edge on the graph, indicative of data transfer or other synchronization event between task instances.

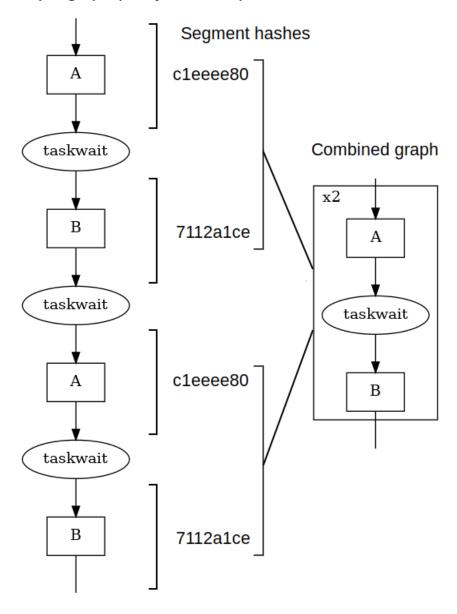

The first step of the analysis involves detecting program "main loop" and averaging loop iterations. This process works by finding vertices that represent "taskwait" synchronization events and dividing the graph into segments delimited by these vertices. A vector of "structural fingerprints" is then computed for these segments by recursively hashing edges and vertices within each segment. The main loop is then identified by searching for repeating patterns in the structural fingerprint vector. Finally main loop iterations are averaged together by averaging the performance metrics associated with each vertex. In the event that main loop identification is not successful, the analysis treats the entire graph as a single iteration (see Figure 3.6).

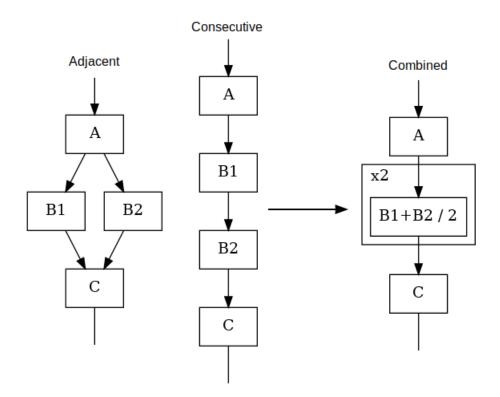

Further folding of the graph is achieved by merging vertices and edges under certain conditions. The first condition is for "adjacent" vertices. A set of vertices are considered adjacent if they share a dependency with a previous task, but not with each other. The second condition is for "consecutive" vertices. Two vertices are considered consecutive if they are identical and one is dependent upon the other. Vertices can only be merged if they represent instances of the same task and have the same number of inputs and outputs of the same size. During merging, task performance information including execution time and operation counts are averaged and the vertex is assigned an iteration count equal to the sum of the iteration counts of the original vertices. Edges are also inspected and merged if the memory ranges attached to them are contiguous. This merging process is applied iteratively to the graph until no further merging opportunities are present.

The final stage of the analysis is the assignment of task code either to the accelerator or to the CPU. This is achieved by a brute-force algorithm which iteratively evaluates the effectiveness of all possible assignments. The evaluation process for any given assignment uses operation counts and graph structure to determine the amount of compute on both the CPU and the accelerator, as well as the amount of CPU-accelerator communication. These quantities are evaluated using a fitness function (see Figure 3.8), and the assignment with the highest fitness is selected. If no assignment scores better than zero, the assignment algorithm assigns the entire task code to the CPU.

Input graph (many iterations)

Figure 3.6. Diagram of main loop detection process.

Figure 3.7. Illustration of vertex merging.

$$f(o_a, o_c, b_{io}) = \begin{cases} \frac{o_a}{b_{io}}, & \text{ if } \frac{o_a}{o_c} > 10\\ 0, & \text{ otherwise} \end{cases}$$

where:

- $o_a =$ Operations on the accelerator.

- $o_c = 0$  perations on the CPU.

- $b_{io} = \text{CPU-accelerator I/O in bytes.}$

Figure 3.8. Task assignment fitness function.

| Representation  | Inputs                          | Outputs                                                              |

|-----------------|---------------------------------|----------------------------------------------------------------------|

| Task graph      | Task graph, ompss task<br>graph | Task graph, total operation count, task<br>summary (csv)             |

| Loop flow graph | Loop flow graph, task<br>graph  | Loop flow graph, total operation count, task summary (csv), dot file |

Table 3.2. Summary of tool inputs/outputs.

#### 3.1.3.5. Output and tool structure

The tools define two representations, a task graph and a loop-flow graph. Each representation can be serialized or deserialized as json. Each representation has an associated executable into which files may be passed to perform conversions between representations and/or output analysis information. Table 3.2 contains a summary of possible analyses and input/output formats for each representation. Some output formats also accept optional parameters. For example, the dot file output representation may optionally include task assignments (shown as blue task outlines) or compute to I/O ratio (shown as red-green gradient coloring on task nodes). During development emphasis was placed on modularity and extensibility to enable the tools to be expanded and repurposed for future projects.

#### 3.1.4. Testing

To test the tools, task-based implementations of three different algorithms were chosen as case studies. These were; n-body simulation, the vgg16 neural network and cholesky matrix decomposition.

#### 3.1.4.1. N-body gravitation simulation

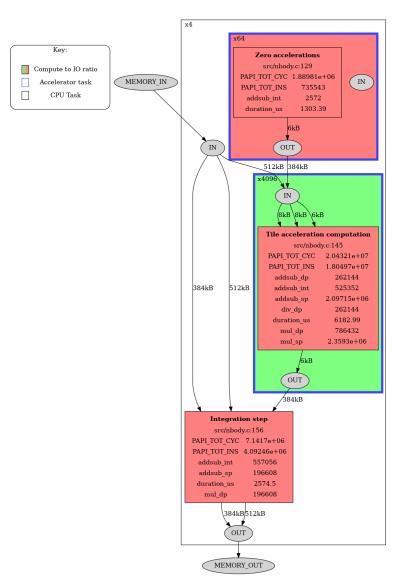

The term N-body refers to a class of algorithms for modeling the motion of sets of particles, typically under the influence of mutual forces. For this test case an n-body gravitational simulation was implemented whereby particles move relative to one another under the influence of mutual gravitation. In each timestep particle positions and velocities are computed based on their relative positions and velocities from the previous timestep. Each timestep is divided into two tasks; the force/acceleration computation stage, which involves computing the acceleration applied to each body as a result of gravitational interaction with each other body, and the integration step which involves updating body positions and velocities with respect to the computed forces/accelerations.

The acceleration computation is by far the most computationally expensive step, with computational complexity  $O(N^2)$  where N is the number of particles. The integration step is inexpensive by comparison with computational complexity O(N). A common strategy when accelerating workloads like this is tiling the acceleration computation loop so that body positions for a tile fit within the processor cache. In this task-based implementation, each tile is given its own task. The graph in Figure 3.2 is the result of analyzing the task graph generated by a 32768 particle simulation with a tile size of 512x512 bodies running for four timesteps.

For this test algorithm, task cost was estimated using the mercurium analysis framework to acquire operation counts on a per-operation-type basis. It can be seen that the majority of operations take place in the acceleration computation step (see Figure 3.9). The assignment generated by the tools suggests computing particle accelerations on the accelerator and integration on the CPU. This is reasonable within a single iteration but in practice the researcher is unlikely to be interested in seeing the results at the end of every timestep. In this case it would become favourable to execute all stages of the computation on the accelerator and only fetch results once the simulation is complete. Unfortunately, nanox is not currently capable of relating data volumes and address ranges to variable names. This means that it isn't possible to identify which memory regions are outputs when the analysis tools are run. Because of this, the tools assume that all output memory ranges at the end of the loop are required outputs. Additionally,

each body-to-body interaction includes a call to the C standard library square root operation that is not included in the operation count total due to it being implemented in a library.

Figure 3.9. Analyzed task graph; 32768 bodies, 512x512 tiles, 4 iterations.

## 3.1.4.2. Image recognition using VGG16

The VGG16 neural network is a convolutional neural network for image classification [37]. The computation involves passing data through multiple layers of computation each with differing characteristics (see Figure 3.10). There are three major data items required to process an image. Image and layer output state, weights and biases. Convolutional layers have a large amount of network state, but a small number of weights and biases as the same values are used for each kernel. By contrast, fully connected layers have a large number of weights but a comparatively small amount of network state. For this implementation of the network, layer computations were chunked into blocks and separate buffers were allocated for the results of each layer.

The assignment algorithm suggests computing the results of convolutional layers on the accelerator and fully connected layers on the CPU. This assignment makes sense as the large quantity of weight data associated with fully connected layers makes them unfavourable. This aligns well with the manual algorithm partitioning discussed earlier (see Figure 3.4).

#### Figure 3.11. VGG16 loop flow graph after analysis.

#### 3.1.4.3. Cholesky matrix decomposition

Cholesky decomposition is a decomposition of a hermitian positive definite matrix into the product of a lower triangular matrix and its conjugate transpose. This process has applications in numerical methods and solving systems of linear equations.

Figure 3.12. Analyzed task graph, choleksy decomposition, 2048x2048 matrix with tile size 256x256.

Unlike VGG16 or n-body examples, the task-based Cholesky matrix decomposition algorithm exhibits a less regular graph structure. Because of this the analysis phase fails to reduce the complexity of the graph appreciably and graphs generated at larger problem sizes still quickly become unintelligible.

## 3.1.5. Limitations and future work

#### 3.1.5.1. Task cost estimation

The static analysis of the source code can provide useful information regarding the operation count, while avoiding any overhead as required by dynamic instrumentation techniques. However it has the following limitations:

- The Mercurium compiler only allows the analysis of one translation unit at a time. This means that, for a given file, the compiler can only access the code in that file and any included header. Inter-procedural analysis is then limited to one translation unit.

- The capability to compute the exact number of operations in a given region depends on the knowledge the compiler can gather about the variables involved in the region. Particularly, the compiler requires knowledge about:

- Variables determining the iteration space of the loops: when these are not known, the accurate expression can still be generated but its exact value will only be known at run-time.

- Variables involved in conditional statements: when these are not known, then only an approximation of the total number of operations can be provided.

- No loop unrolling is performed to obtain the operation count. As a consequence, there are limitations on the type of code that can be analyzed successfully by this phase. Particularly, only loops in the canonical form for (init-expr; test-expr; incr-expr) structured-block are accepted.

- Currently, conditional statements (e.g., if-else statement) are just approximated, i.e., the number of operations of the statement is always computed to the maximum number of operations of any of the possible branches, unless the condition always evaluates to the same value and it is known at compile-time.

• Several features of advanced versions of C++ are not supported in the analysis, e.g., lambda expressions, range-based loops and concurrency.

As part of future work, the plan is to:

- Provide a more accurate solution for conditional statements.

- Support more complex loops like while-loops.

- Accept information from the user regarding functions that are called in the source code which code is not available at compile time. This could be in the form of annotations associated with the source code, or a separate template-file with the function headers and the expected number of operations of each type.

#### 3.1.5.2. Task graph analysis

The analysis tool has shown the capacity to reduce the redundancy of plain task graphs considerably, with excellent results when applied to data parallel algorithms with regular task graphs like the n-body and vgg16. However testing exposes a number of limitations:

- Irregular graphs like those produced by cholesky decomposition are handled poorly by the analysis. Investigation of improved methods for detecting repetitive structures in the graph both for main loop detection and folding of less regular graph structures remains as future work.

- Variable names are not attached to data ranges. This prevents the possibility of suggesting/analyzing more complex strategies like loop unrolling, a common strategy on FPGAs to optimise I/O and memory bandwidth. The lack of this feature is primarily due to limitations in the nanox instrumentation API and could conceivably be solved through use of an alternative instrumentation technique, or by further extending the API.

- Main loop detection is error prone and expects main loops to be delimited by synchronisation events. This may not be the case for all algorithms and generally cannot be assumed. More general ways to detect repetitive graph structures remain as future work.

- Output graphs sometimes have confusing layouts due to graphviz's dot layout engine. Currently the dot file output for the loop flow graph exercises no control over the layout of vertices during rendering. By manually adding rank allocations for vertices, it may be possible to further improve the readability of output graphs. This also remains as future work.

- Instrumented programs have to be executed with a single worker thread because of the manner in which the nanox runtime handles dependencies between tasks. This limits the usage of the tools in their current state to the instrumentation of programs at fairly small problem sizes. Solving this issue remains as future work.

- Concurrent and commutative sections are currently not supported by the nanox instrumentation plugin developed for the project. Supporting these features of the programming model remains as future work.

In conclusion, the proof of concept analysis techniques implemented for this project show that it is possible in many cases to analyze/reduce large task graphs and achieve useful insights into program structure, but that substantial work remains to be done to develop the technique to a point where it is usable for a wide variety of input programs.

#### 3.2. Enhanced XiTAO Data Parallel Interface

In this deliverable, we explain the enhancements provided on top of the XiTAO data parallel interface. As highlighted previously in D4.3, XiTAO incorporates modern C++ compiler technology to deliver a DAG-friendly data parallel interface. With this interface, many applications that consist of parallel Single Program Multiple Data (SPMD) regions can leverage the backend features offered by the XiTAO RT including energy efficiency and interference awareness depicted by WP3.

```

// tao width: XiTAO specific resource hint

1

// i: the loop counter

2

// loop_start: loop iterator start

3

// loop_end: loop iterator end

4

// scheduling_type: XiTAO scheduler type (e.g. dynamic)

5

6

// block length: the chunk size for each task

7

auto dataparallel_nodes = __xitao_async_data_parallel_region

8

(tao_width, i, loop_start, loop_end,

9

scheduling_type, block_length,

10

for (int j = 0; j < N; j++) {</pre>

11

C[i][i] = 0;

12

for (int k = 0; k < N; k++)

13

C[i][j] += A[i][k] * B[k][j];

14

}

15

);

16

17

for(int i = 0; i < dataparallel_nodes.size(); ++i) {</pre>

18

previous node[i]->make edge(dataparallel nodes[i]);

19

}

20

21

for(int i = 0; i < dataparallel_nodes.size(); ++i) {</pre>

22

next_node[i]->make_edge(dataparallel_nodes[i]);

23

}

24

```

Figure 3.13. The basic structure of a DAG based program inserting SPMD code regions

The interface makes it possible to indicate a resource hint that the runtime can use to aggregate resource to a specific task within the loop or a set of tasks (resource moldability). Here, we make the distinction between the asynchronous and synchronous modes of executions.

The data-parallel frontend depicted here resides on top of the XiTAO Energy Efficient Scheduler (EAS), which is evaluated in Deliverable D3.4. EAS is an energy efficient work stealing runtimes targeting modern platforms with asymmetric cores and cluster-based DVFS (e.g. NVIDIA Jetson TX2), as well as symmetric homogeneous platforms. The scheduler estimates the energy consumption on a per-task level and performs task placement decisions for each task to minimize the energy consumption. Deliverable D3.4 evaluates several alternatives in the design of the XiTAO's energy efficient scheduler and has the following characteristics:

- 1. Task type-awareness that is important to select the most efficient resources for each task instance;

- 2. Utilizing an exponential backoff sleep strategy, which helps reduce energy waste from work stealing loops with minimal impact on performance;

- 3. Adaptive task moldability that can further improve energy efficiency by reducing resource over-subscription and inter-task interference.

## 3.2.1. The Asynchronous Data Parallel Mode

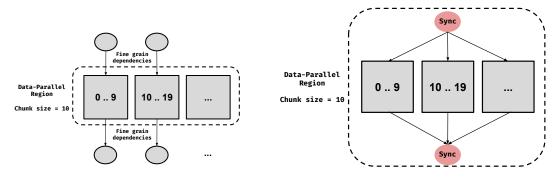

This mode arises from the assumption that programs can be expressed as DAGs with different granularities. One of the main motivations behind the inclusion of async data parallel nodes is the fact that task loops can then be seamlessly inserted into task graphs (see Figure 3.14a), and will benefit from reducing the overhead of fork-join programming approaches and achieve energy-efficiency from the runtime backend. The snippet on Figure 3.13 shows how a loop parallel region, for example, can be part of a full DAG structure using the XiTAO programming interface. Also, Table 3.3 highlights the interface parameters. The capability of nesting loop parallel nodes in a DAG workflow has been supported. Also, a few explanatory benchmarks adopted from Ro-

(a) Asynchronous mode with fine-grain dependencies

(b) Synchronous mode that is analogous to fork-join models

Figure 3.14. XiTAO data parallel modes

Figure 3.15. The basic structure of a DAG based program inserting SPMD code regions

dinia Benchmark Suite and Barcelona OpenMP Task Suite have been developed and will soon appear in the XiTAO online repository.

| Parameter  | Usage                                                              |

|------------|--------------------------------------------------------------------|

| width      | The XiTAO resource hint to be given to the loop tasks.             |

| iter       | The loop index/iterator.                                           |

| end        | The loop end.                                                      |

| sched      | The scheduling options (e.g., static, dynamic, energy-aware, etc.) |

| block_size | Governs the granularity of task creation.                          |

Table 3.3. The parameters input by user to the XiTAO's asynchronous data parallel interface

## 3.2.2. The Synchronous Data Parallel Mode

The sync data parallel mode is semantically equivalent to OpenMP/OmpSs taskloops, and mainly supported for backward compatibility of legacy codes. In this mode, operation happens in 3 steps, shown in Figure 3.14b). First, the DAG execution of previous nodes is synced. Second, the loop is divided into chunks of tasks according to the block\_length parameter. Third, an implicit wait is inserted to pause the execution until all loop tasks have finished. Listing 3.15 shows an example of such usage.

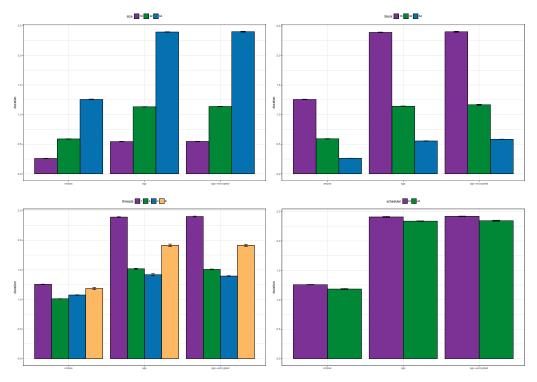

## 3.2.3. Evaluation of the Alya solver

The most time consuming part of Alya code is the solution of the Poisson equation. The procedure consists in solving a linear system of equations in each time integration step. The matrix of the system is a laplacian, and has as many rows as the number of cells used in the discretization of the computational domain. For the smart city use case, the matrix remains constant during the full simulation, therefore the pre-processing operations are negligible. The iterative solvers are the best option to solve the system due to its low memory footprint when compared with direct solvers. The Preconditioned Conjugate Gradient (PCG) is the iterative solver most commonly used in Alya. The solver is mainly composed of three algebraic operations: vector operations (axpy and dot) and the sparse matrix vector multiplication (spmv). The operations are memory

bounded, and its implementation consist of a loop of the size of rows of the matrix. This configuration enables using directive-based models or run-times that automatically parallelize that loop. Four implementations of the solver have been evaluated using different components of the LEGaTO tool-chain.

- **OpenMP**: GCC version 7.4, loop-based, using parallel for directives

- **OpenMP taskloop**: GCC version 7.4, using parallel taskloop directives

- OmpSs-2: OmpSs-2 version 2020.09, using tasking

- XiTAO: xitao vo.8-alpha

- CUDA: version 10.0 is used, axpy and dot operations are linked with the cublas library.

The experiments have been performed on the NVIDIA Xavier nodes provided by Bielefeld. The solver was executed on matrix systems obtained from Alya execution using unstructured meshes with sizes ranging from 100,000 to 1,600,000 rows. In these matrices, the number of non-zero elements per row is less than five and oddly distributed due to the unstructured meshes. The sequential execution has been included as a baseline. Parallel executions have been obtained using 8 cores for the SMP models, and CUDA 10.0 for the execution on the GPU. The execution time of the solver for the different models is shown in Table 3.4.

| Matrix    | Sequential | OpenMP | OmpSs | Xitao | OpenMP   | CUDA |

|-----------|------------|--------|-------|-------|----------|------|

| Size      |            |        |       |       | taskloop |      |

| 50,000    | 0.47       | 0.13.  | 0.27  | 0.35  | 0.64     | 0.17 |

| 100,000   | 1.11       | 0.24   | 0.48  | 0.69  | 1.40     | 0.29 |

| 200,000   | 2.38       | 0.48   | 0.85  | 1.41  | 2.77     | 0.42 |

| 400,000   | 7.63       | 1.32   | 2.05  | 4.32  | 10.13    | 1.07 |

| 800,000   | 17.64      | 3.14   | 4.22  | 9.98  | 22.85    | 2.18 |

| 1,600,000 | 48.35      | 8.56   | 11.04 | 27.30 | 61.03    | 5.64 |

Table 3.4. Time in seconds for the different executions of Alya's solver.

The best cases for each matrix size are highlighted in bold. Note that for matrix sizes with less than 200,000 rows, the OpenMP version is the most efficient implementation with a speedup of 3.6 times with respect to the sequential version. On the other hand, from 200,000 rows and above, the CUDA implementation is the most efficient one with a speedup of up to 8.5 times with respect to the sequential case. CUDA implementation does not perform well with small matrix sizes due to two factors: i) the GPU requires of certain occupancy in order to exploit the maximum memory bandwidth that is hard to achieve with the sparsity pattern of our matrices, and ii) the GPU time includes memory transfers of the right hand side (r.h.s) and resulting vectors from host to device, the relative weight of those transfers is higher in the smaller cases. Anyhow, the workload in the final smart cities use case ranges from 1,000,000 to 4,000,000 per node, being in the range in which the GPU implementation is the most efficient one.

Among the CPU-only executions, OpenMP loop-based implementation is the most efficient code for all the matrix sizes. In the range of the smart city use case, OpenMP outperforms OmpSs by a 28% and XiTAO by a 318%. The drop of performance with OmpSs tasking is caused by the lower data locality achieved, compared to OpenMP for loops. Additionally, it is important to note that the XiTAO data-parallel interface is semantically similar to the OpenMP taskloop, and it loses some performance to achieve energy efficiency as was shown in D3.4. Hence, a more fair comparison with XiTAO loops would be considering the taskloop implementation of OpenMP, since XiTAO uses a similar strategy to associate threads with task DAGs. For the largest case, XiTAO is 2.2 times faster than OpenMP taskloop based implementation, and is consistently faster in the other cases.

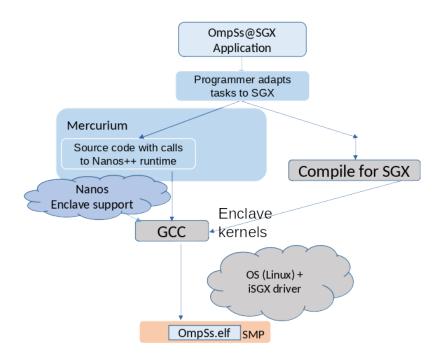

Figure 3.16. Intel SGX applications with OmpSs support.

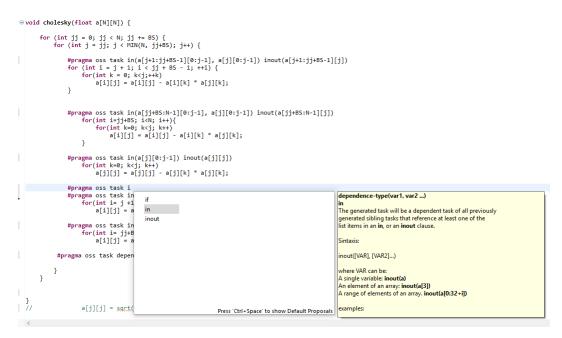

# 3.3. OmpSs Integration with SGX

Figure 3.16 depicts the proposed approach by showing how the combination of OmpSs programming model with Intel SGX can be performed. First, the programmer has to adapt the tasks to SGX which means defining the tasks as C/C++ functions which will be declared and implemented using the Enclave's interface. Then, the parallelization pragmas can be added to the secure application in the same way as it is done for non-secure application except that all the pragmas have to be placed outside the Enclave. For instance, if the user wants to annotate a function declared inside the Enclave then the pragmas have to be placed on the function call instead of declaration. Finally, the annotated code is compiled using the Mercurium compiler and the Nanos++ runtime schedules the application tasks on the platform.

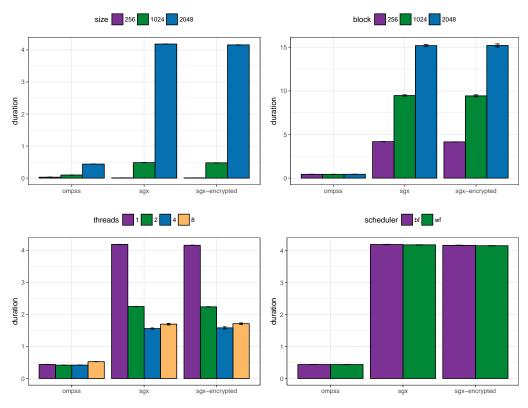

We evaluated the proposed approach by means of four benchmarks consisting of cholesky factorization, dot product, matrix multiplication and two versions of the STREAM benchmark. We analyze each of these applications in the following 3 versions: a pure OmpSs implementation, an implementation combining OmpSs and SGX, and a third one adding encryption on top of the OmpSs and SGX combination. All the applications used here take as input a matrix and the parallelization is done based on the blocks of this input matrix. Considering that, the size of a given input matrix indirectly defines the graph size. i.e., the number of total tasks spawned. Moreover, the block size in which we split the matrix defines the input size of each task as the larger a given block is the more data has to be processes by a given task. We then evaluate how each version performs when we vary the matrix and block size as well the scheduling algorithm. Finally, We also vary the number of threads to see how the applications scale for multiple threads.

We deploy our experiments on a cluster of 4 quad-socket Intel E3-1275 CPU processors with 8 cores per CPU, 64 GiB of RAM and 480 GB SSD drives. The machine runs Ubuntu Linux 20.04.1 LTS on a switched 1 Gbps network. Power consumptions are reported by a network connected LINDY iPower Control 2x6M Power Distribution Unit (PDU), which we query up to every second over an HTTP interface to fetch up-to-date measurements for the active power at a resolution of 1W and 1.5% precision.

#### Cholesky Kernel.

The Cholesky Kernel is a decomposition of a Hermitian, positive-definite matrix into the product of a lower triangular matrix and its conjugate transpose. The kernel uses four different linear algorithms: potrf, trsm, gemm and syrk. The way we parallelize the code is by annotating these kernel functions so that each call in the previous loop becomes the instantiation of a task. The

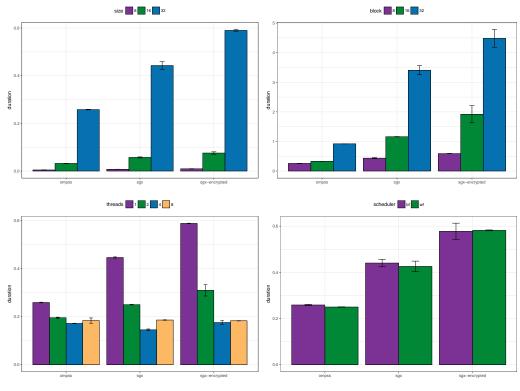

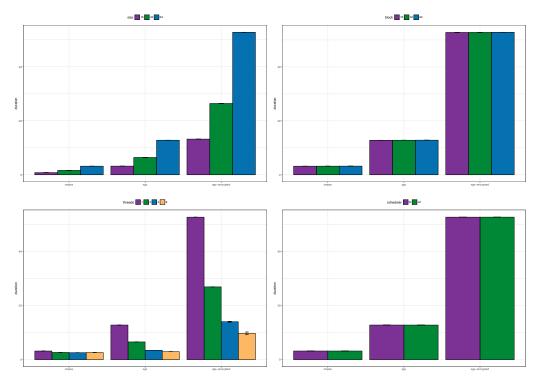

Figure 3.17. Evaluation results for Cholesky Kernel application.

original application used these algorithms from the MKL or OpenBLAS linear algebra libraries, and, in order to have the algorithms available inside the enclave without dependences on Linux services we have provided the four algorithms in source code inside the application itself.

Figure 3.17 shows the comparison of the results of the application. Comparing results when varying the matrix size (plot on the top-left), we can observe that the overhead when using SGX and SGX with encryption is noticeable (7x slowdown). Nevertheless encryption does not introduce overhead compared to the non-encrypted version. Regarding the influence of the block size, results (plot in the top-right) show that when the block size if larger, the overhead is also larger. Regarding the number of threads (plot in the top-right), it shows that the execution time scales better when using SGX and SGX with encryption, due to the fact that each task has more work to do, and thus, the overhead of the runtime is reduced in comparison. Finally, the OmpSs scheduling policy (plot on the bottom-right) has no impact on the performance. Both breadth-first and work-first (Cilk-like policy) give the same performance.

#### Dot Product

The dot product is an algebraic operation that takes two equal-length sequences of numbers and returns a single number obtained by multiplying corresponding entries and then summing those products. A common implementation of this operation accumulates the result of each iteration on a single variable. This kind of operation is called reduction, and it is a common pattern in scientific and mathematical applications.

There are several ways to parallelize operations that compute a reduction but in our implementation we use a vector to store intermediate accumulations. This means that tasks operate on a given position of the vector and the parallelism is determined by the vector length. Finally, when all the tasks are completed then the contents of the vector are summed up.

Figure 3.18 shows the experimental results for the 3 versions of this application. In this case we observe an overhead between 2x and 3x on the SGX and SGX Encryption versions when compared with pure OmpSs implementations. Regarding the scalability of applications, for the parameters values chosen the input size does not seem to impact performance. When it comes to number of threads, for this given application the optimal solution is 2 threads which is at least 15% faster

Figure 3.18. Evaluation results for Dot Product application.

Figure 3.19. Evaluation results for matrix multiplication application.

than the sequential version. However, with 4 and 8 threads the performance starts to decrease again and this can be due to the overhead added when compared with the size of tasks.

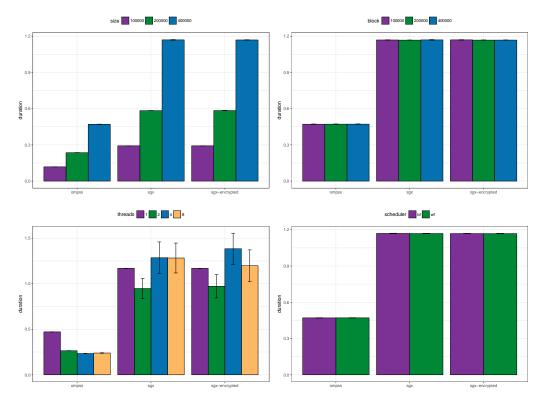

#### **Matrix Multiplication**

The matrix multiplication application receives matrix A and matrix B as input, performs the mul-

Figure 3.20. Evaluation results for STREAM application (barrier based version).

tiplication calculations between A and B, and outputs the result in a third matrix C. Figure 3.19 shows the experimental results for the 3 versions of this application. In this context, we observe at least 1.5x to 2x overhead for the SGX and SGX plus encryption versions when compared to the pure OmpSs version, respectively. However, all three applications scale well when a smaller input sizes is used and more threads are added. In fact, the both SGX versions present at least 2x improvement when using multiple threads when compared with their respective sequential versions while the pure OmpSs version only present up to 25% improvement. With this we can conclude that although there is a clear trade-off between performance and security, we can easily minimize the extra cost of adding a security layer by combining SGX with OmpSs.

#### STREAM benchmark

The STREAM benchmark [6] is a simple synthetic benchmark program that measures sustainable memory bandwidth (in GB/s) and the corresponding computation rate for simple vector kernel. We present the following two versions of this application: one that inserts barriers and another without barriers. The behavior of the version with barriers resembles the OpenMP version, where the different functions (e.g., Copy, Scale) are executed one after another for the whole array. In the version without barriers, functions that operate on one part of the array are interleaved and the OmpSs runtime keeps the correctness by means of the detection of data-dependences.