# D<sub>5.3</sub> "Final report on development and optimization of use-cases and integration"

Version 1.1

# **Document Information**

| Contract Number      | 780681                                                                                                                                                                                                                                                           |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Project Website      | https://legato-project.eu/                                                                                                                                                                                                                                       |  |  |

| Contractual Deadline | 30. November 2020                                                                                                                                                                                                                                                |  |  |

| Dissemination Level  | Public                                                                                                                                                                                                                                                           |  |  |

| Nature               | Report                                                                                                                                                                                                                                                           |  |  |

| Author               | Micha vor dem Berge (CHR)                                                                                                                                                                                                                                        |  |  |

| Contributors         | Nils Kucza (UBI), Erik Funke (CHR), Dirk Michels (CHR), Felix Wiesenmüller (CHR), Raúl de la Cruz (BSC), Xavier Martorell (BSC), Sigrun May (HZI), Amani Al-Mekhlafi (HZI), Frank Klawonn (HZI), Hans Salomonsson (MIS), Daniel Ödman (MIS), Tobias Becker (MAX) |  |  |

| Reviewers            | Amani Al-Mekhlafi (HZI),<br>Leonardo Bautista Gomez (BSC),<br>Jens Hagemeyer (UBI)                                                                                                                                                                               |  |  |

The LEGaTO project has received funding from the European Union's Horizon 2020 research and innovation programme under the Grant Agreement No 780681

# Changelog

| Version | Date       | Description of Change                                                                                                                                                            |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VO.1    | 29.08.2020 | Initial ToC, based on D <sub>5.2</sub>                                                                                                                                           |

| V0.2    | 27.10.2020 | First input for chapters 2, 3 and 5                                                                                                                                              |

| vo.3    | 05.11.2020 | First input for chapters 4, 6, 7 and 8 merged                                                                                                                                    |

| vo.4    | 06.11.2020 | Merged version with updates in chapters 3 and 4                                                                                                                                  |

| vo.5    | 09.11.2020 | Updates of chapters 5, 6, 7                                                                                                                                                      |

| vo.6    | 13.11.2020 | Internal review ready                                                                                                                                                            |

| VO.7    | 25.11.2020 | Updates of all chapters, working on the internal review comments                                                                                                                 |

| vo.8    | 27.11.2020 | Pre-final version, merging all updates from partners                                                                                                                             |

| V1.0    | 30.11.2020 | Final version                                                                                                                                                                    |

| V1.1    | 05.02.2021 | Fix of broken link, add table of metrics to conclusion, harmonise metrics in use cases, add components overview to smart city, add metrics to executive summary, add Chapter 4.6 |

# Index

| 1 | Ex  | kecutive Summary5                                                   |          |  |  |  |  |

|---|-----|---------------------------------------------------------------------|----------|--|--|--|--|

| 2 | Int | roduction                                                           |          |  |  |  |  |

| 3 | Sm  | nart Home                                                           | <u>9</u> |  |  |  |  |

|   | 3.1 | Hardware evaluations and performance analysis with YOLO and Darknet | 10       |  |  |  |  |

|   | 3.2 | Smart Mirror Prototype Hardware Setups                              | 1        |  |  |  |  |

|   | 3.3 | Smart Mirror Software Optimization Progress                         | 12       |  |  |  |  |

|   | 3.4 | Baseline Benchmark and Performance                                  | 1/       |  |  |  |  |

|   | 3.5 | Development of additional Features                                  | 15       |  |  |  |  |

| 4 | Sm  | nart City                                                           | 2        |  |  |  |  |

|   | 4.1 | Metrics & Optimization Goals                                        | 2        |  |  |  |  |

|   | 4.2 | Baseline Benchmark                                                  | 2        |  |  |  |  |

|   | 4.3 | Development Status & Optimization Path                              | 25       |  |  |  |  |

|   | 4.4 | Final numerical results                                             | 27       |  |  |  |  |

|   | 4.5 | A low energy-consumption Alya-oriented cluster                      | 29       |  |  |  |  |

|   | 4.6 | Increase robustness for Alya at large scale                         | 30       |  |  |  |  |

| 5 | Inf | ection Research                                                     | 3        |  |  |  |  |

|   | 5.1 | Description of the accelerated biomarker discovery workflow         | 3        |  |  |  |  |

|   | 5.2 | Metrics & Optimization Goals                                        | 35       |  |  |  |  |

|   | 5.3 | Benchmarks                                                          | 35       |  |  |  |  |

| 6 | Ma  | achine Learning                                                     | 40       |  |  |  |  |

|   | 6.1 | Metrics & Optimization Goals                                        | 40       |  |  |  |  |

|   | 6.2 | Optimisation                                                        | 40       |  |  |  |  |

|   | 6.3 | Integration                                                         | 42       |  |  |  |  |

|   | 6.4 | Experiments Setup                                                   | 42       |  |  |  |  |

|   | 6.5 | Results                                                             | 43       |  |  |  |  |

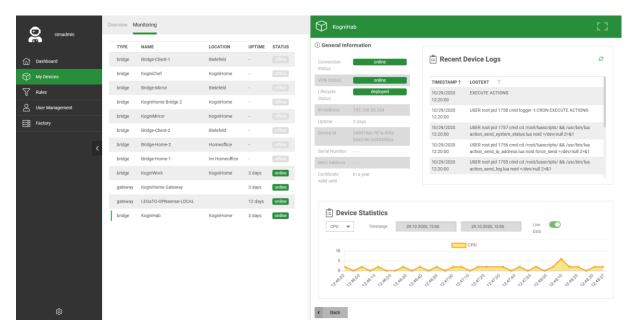

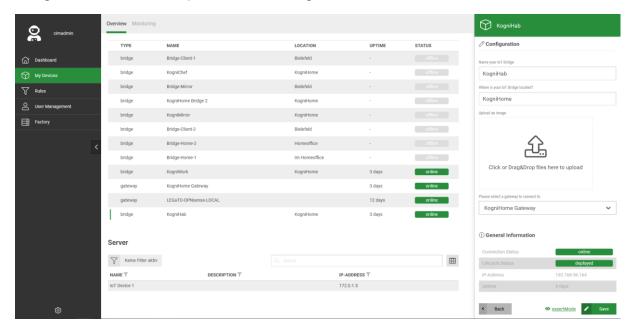

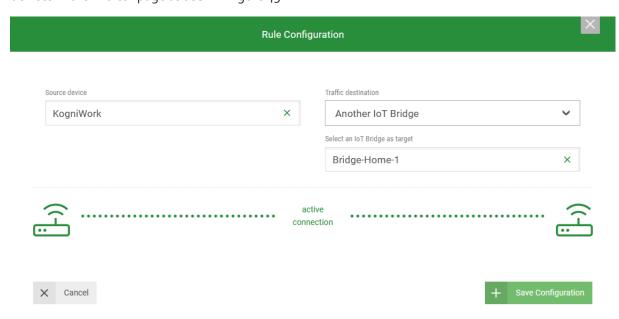

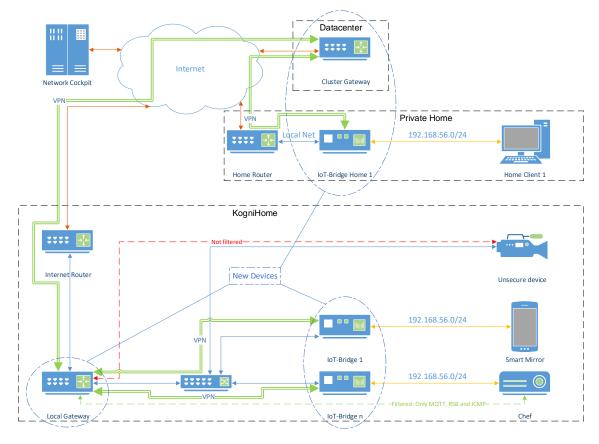

| 7 | Se  | cure IoT Gateway                                                    | 47       |  |  |  |  |

|   | 7.1 | Components                                                          | 48       |  |  |  |  |

|   | 7.2 | Integration in the Smart Home use-case                              | 55       |  |  |  |  |

|   | 7.3 | Benchmarks                                                          | 57       |  |  |  |  |

| 8 | Ov  | verall project integration                                          | 62       |  |  |  |  |

|   | 8.1 | OmpSs and XiTAO targeting SMP tasking                               | 62       |  |  |  |  |

|   | 8.2 | OmpSs with support for CUDA and OpenCL kernels                      | 62       |  |  |  |  |

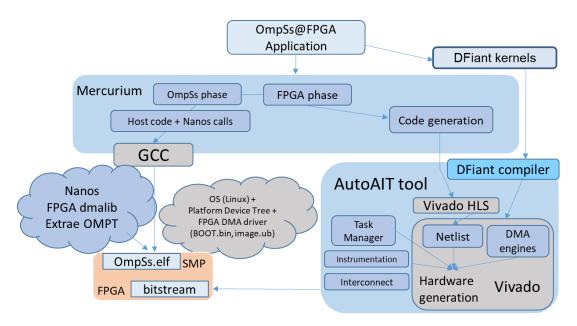

|   | 8.3 | OmpSs with support for Xilinx FPGAs and DFiant kernels              | 66       |  |  |  |  |

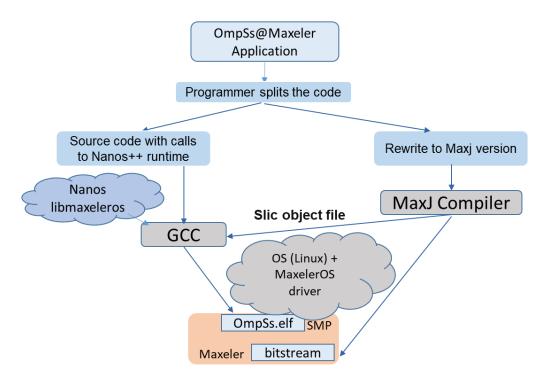

| 8.  | 4    | OmpSs with support for Maxeler DFEs     | 68 |

|-----|------|-----------------------------------------|----|

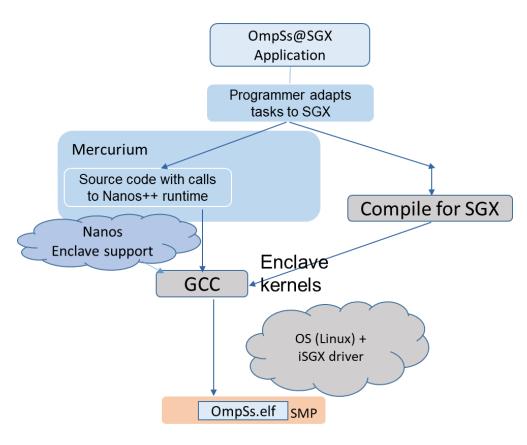

| 8.  | 5    | OmpSs with support for Secure SGX tasks | 70 |

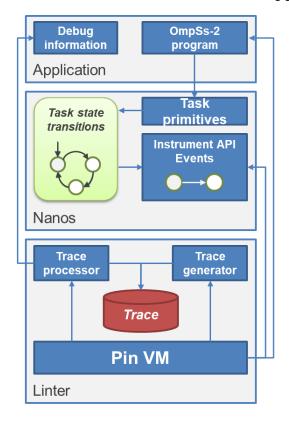

| 8.6 | 6    | Linter tool for OmpSs                   | 72 |

| 8.7 | 7    | IDE plugin for OmpSs                    | 72 |

| 8.8 | 8    | RECS Master and Slurm                   | 73 |

| 9   | Con  | clusion                                 | 75 |

| 10  | Refe | erences                                 | 77 |

# 1 Executive Summary

The main focus of Workpackage 5 is the development and optimisation of different real use cases with the help of the LEGaTO workflow. The final development and optimisation status is reported within this deliverable. There are five different use cases

- 1. Smart Home

- 2. Smart City

- 3. Infection Research

- 4. Machine Learning

- 5. Secure IoT Gateway

All of them except the latter have been optimised using one of the toolflows that the LEGaTO project provides. OmpSs was extended to make use of additional compilers and runtimes as described in chapter 8, so the use cases didn't have to implement all of them in a different way.

The Smart Home use case concentrates on a Smart Mirror demonstrator of which three versions have been developed within the project. A first demonstrator was built, after that, a second enhanced demonstrator was built with many manual improvements that have been carried out, also better standard hardware was used. Finally, the third demonstrator was built, based on the developed LEGaTO edge server, increasing the energy efficiency (measured in FPS/Watt) by 12x.

The Smart City use case simulates the air quality in urban areas. Existing code has been ported from Fortrango to C, now running on x86 as well as ARM64 architectures. An implementation on an FPGA has been developed, showing an energy efficiency increase by a factor of 9, measured in GFLOPS/Watt. A further implementation on an Nvidia Xavier microserver was developed, increasing the energy efficiency by 95x (GFLOPS/Watt) at a cost of an 11x slowdown (wall time in seconds), compared to a BSC Marenostrum4 node. A full-size simulation run takes a total amount of ~1.3 kWh of energy, but as it runs multiple times a day with new input data, there is a lot of optimisation potential.

The Infection Research use case uses statistical methods to research on the effectiveness of drugs, vaccination strategies and harmfulness of pathogens. The major problem of this use case are the extremely long runtimes. To reduce this, four major compute kernels were identified and optimised, resulting in a wall time (in seconds) speedup of 10x, 40x, 544x and about 2503.6x for these kernels. Also, the total energy consumption in Joule for each compute kernel was measured and compared, resulting in a maximum energy efficiency increase of 7708.8 x. A full run with a real dataset using the initial version of the biomarker candidate subset selection would take more than 1.5 years and consume around 187 kWh, so there is a huge potential in both, speed and energy efficiency improvements.

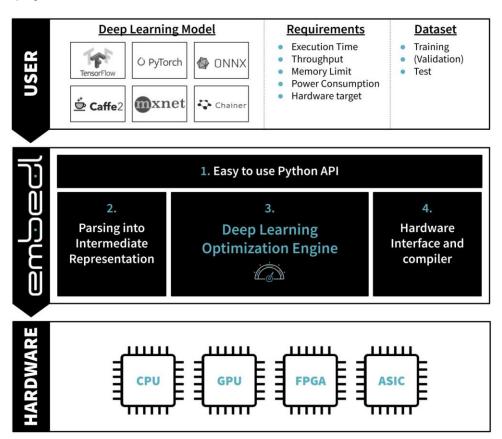

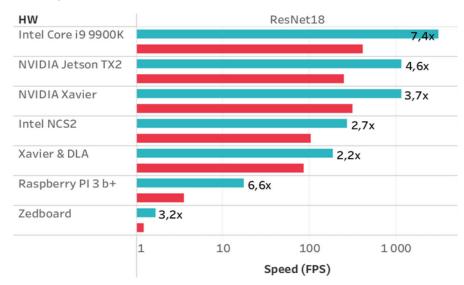

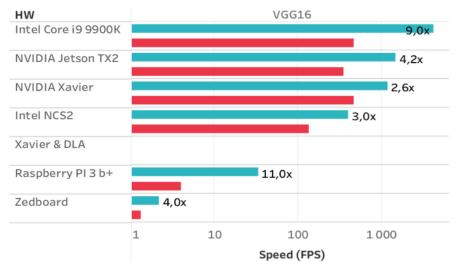

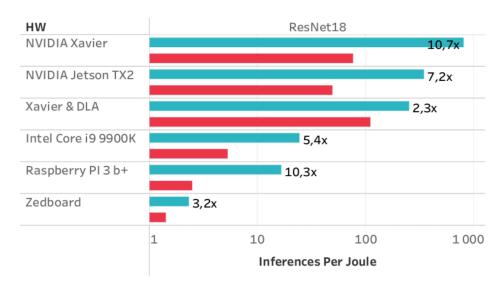

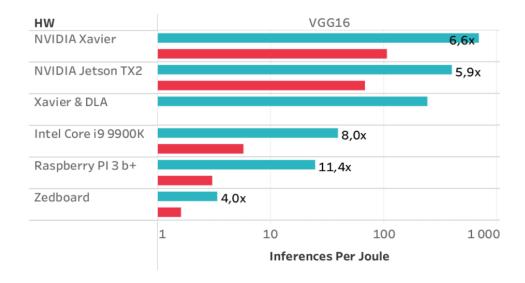

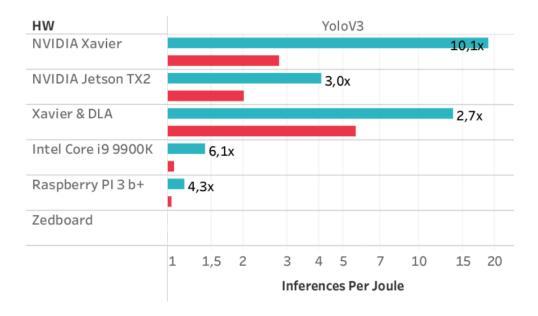

The Machine Learning use case on the one side develops neural networks with a focus on automotive usage, but also optimises existing neural networks with a new kind of deep learning optimisation tool called EmbeDL. With the help of EmbeDL, well known neural networks could be optimised to reach an average speed up of 4.3x (FPS) and energy efficiency increase by 6.3x (measured in inferences per Joule).

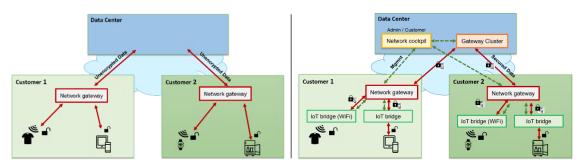

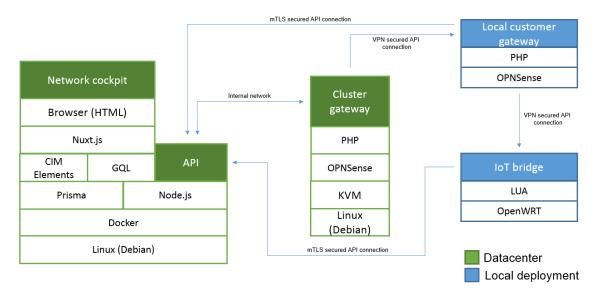

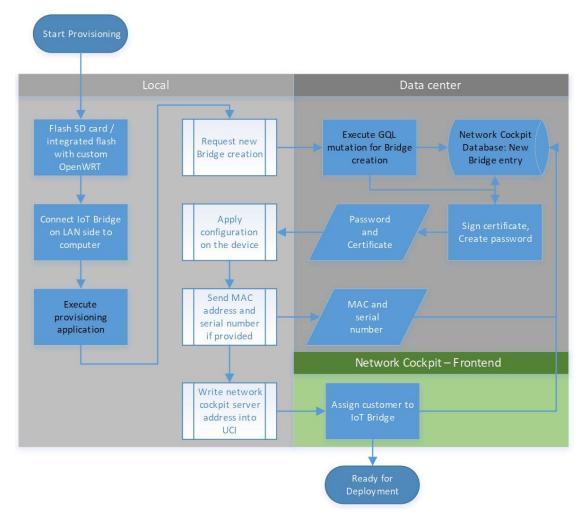

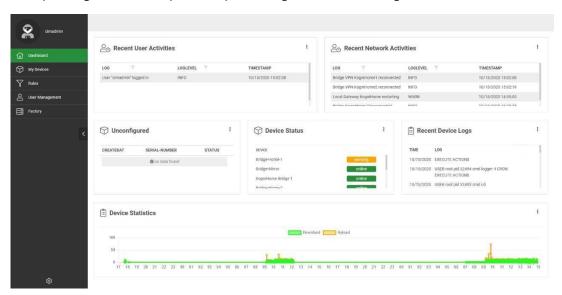

The Secure IoT Gateway makes it easy to secure many types of network connections to and from IoT devices. It bases on well-established technologies like OpenVPN, OPNsense and OpenWrt and adds an easy to use configuration Web GUI and rollout mechanisms on top of it. As analysis of the used components did not reveal any optimisation possibilities for computation speed or energy efficiency, this use case was used to enhance the security for the Smart Home use case.

LEGATO D5.3 Version 1.1 5 / 81

Almost all targeted improvements in the six targeted disciplines energy efficiency, MTBF, code base security, designer productivity, TCO/costs and latency were reached, please see Table 17 in the Conclusion section.

### 2 Introduction

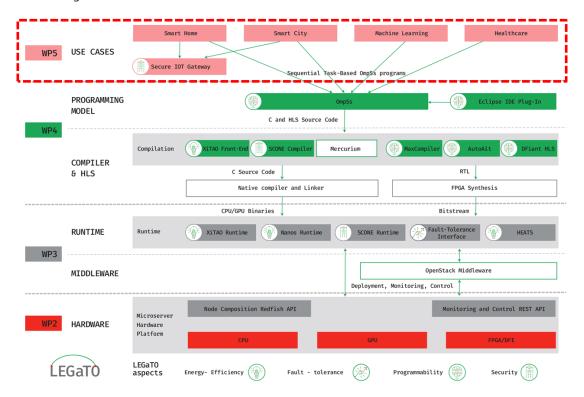

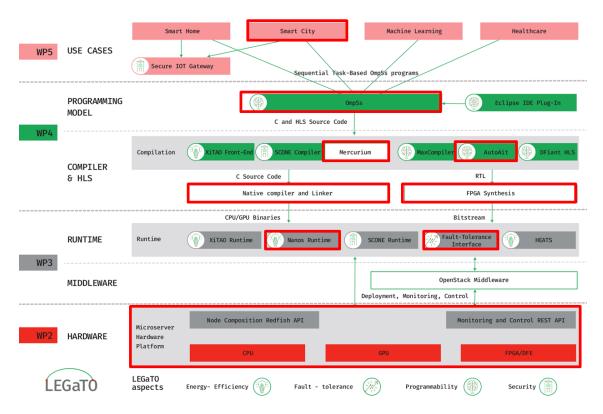

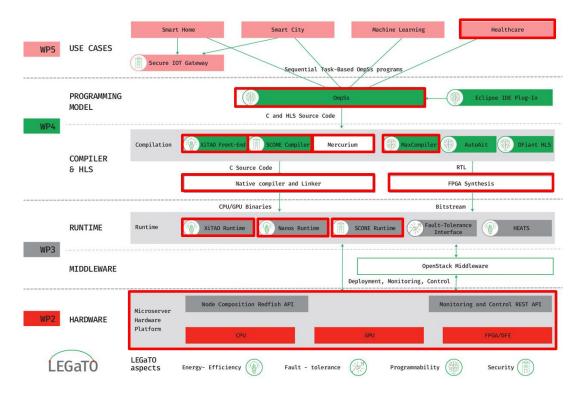

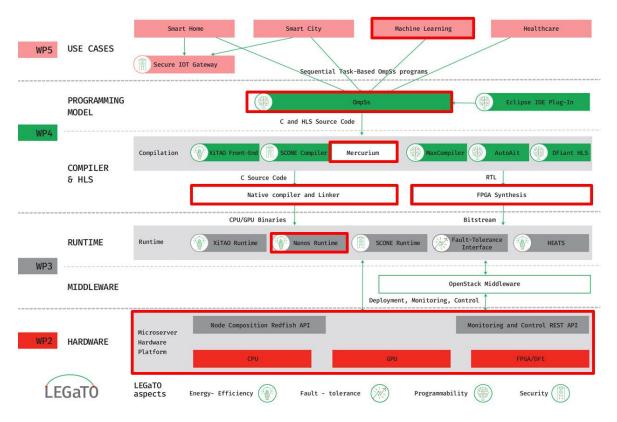

This document presents the final state of the implementation, optimisation and measurements of improvements of the LEGaTO use cases, representing the work carried out in Work Package 5 as shown in Figure 1.

Figure 1: WP5 and the LEGaTO stack

In general, the four use cases of Smart Home, Smart City, Infection Research and Machine Learning have the goal to improve in terms of diverse metrics, such as energy efficiency, as mentioned below – while the Secure IoT Gateway focusses on adding extra security to other use cases. To improve on the diverse metrics, the use cases have been deeply analysed for their requirements and computational characteristics as presented in the first deliverable D2.1 [1]. Based on that, in D5.2 [2] baseline measurements and first optimisations of the use cases were presented, most of them could be massively improved and extended in this document. This deliverable is accompanied by D5.4 [3], the "Report on evaluation of efficiency and TCO improvements of use-cases" in which a detailed analysis of the efficiency and TCO improvements of all use cases is given.

Some use cases have been firstly optimised by hand, e.g. by porting it to a different programming language or by improving the algorithms itself. These optimisations showed already good results, e.g. in the Smart Mirror demonstrator of the Smart Home use case. As a second step, the already hand optimised algorithms were then improved by using one of LEGaTO's main programming models, compilers and runtimes: OmpSs, XiTao, DFiant, MaxJ as well as SCONE.

The optimisation targets of LEGaTO that we are targeting for are the following, as already depicted in D<sub>2.1</sub> and D<sub>5.2</sub>:

- 1. Improve Energy Efficiency

- 2. Increase MTBF (by 5x)

- 3. Increase code base security (by 10x)

- 4. Increase designer productivity (by 5x)

In addition, we also consider the following objectives. These are not explicitly stated as objective in the DoA but are also relevant:

- 5. Reduce TCO/costs

- 6. Reduce Latency

The use cases were optimised using these programming models, compilers, runtimes and optimisation objectives:

|   | Programming Model    | Smart<br>Home | Smart<br>City | Machine<br>Learning | Infection<br>Research |

|---|----------------------|---------------|---------------|---------------------|-----------------------|

|   | OmpSs, XiTao, DFiant | 1,4,5,6       | 1,2,4,5       | 1,4,5,6             | 1,4,5                 |

|   | MaxJ                 |               |               |                     | 1,4,5                 |

| _ | SCONE                |               |               |                     | 3                     |

Table 1: Implemented optimisations and used programming models for the use cases

The structure of this document is quite simple, as every use case has its own chapter. In each chapter, a short introduction of the specific use case is given, followed by description of the optimisation process and measurements to show the improvements.

In case of the Secure IoT Gateway, the four main components and their features are described, as well as some benchmarks under different conditions and loads. Furthermore, the integration into two different locations of the Smart Home use case is described.

An important part of the project was the overall integration, showing that the used and improved LEGaTO frameworks could be used in the use cases, and are making use of the existing and newly developed heterogeneous hardware. This overall integration work is described in chapter 8.

The document finalises with a conclusion.

## 3 Smart Home

Current smart living environments are based on the simple automation of subsystems consisting of sensors, information processing, and actuators. New approaches are mainly driven by large enterprises, pushing big-data approaches, collecting as much information about the user as possible to derive the current action, and anticipating future behaviour. The development of assisted living can be seen as a move from isolated applications realized as simple embedded systems, towards cyber-physical systems gathering and processing large amounts of data from a high number of distributed smart devices. Additionally, the smart home must process interaction of different users simultaneously; conflicting actions have to be recognized (e.g., one user opening a window and another one closing it again) and compromises can be suggested. Different interaction schemes can be combined adaptively, e.g., switching from touch to speech interaction while cooking or using text-based output while phoning. Providing this functionality is highly computationally intensive. Since the collected data contains personal and highly sensitive information, cloud-based processing is undesirable. To address these privacy issues, we target resource-efficient edge computing.

In smart home environments, the smart mirror is a more and more frequently used interface for interaction. It is based on a display with a semi-transparent foil applied on it. This device shows personalized information and enables controlling of other smart components and services, e.g., operating the automated wardrobe, turning on/off the lights or opening/closing the entrance door. For this use case a demonstrator based on the open source project MagicMirror<sup>2</sup> [4] is developed and extended with the most needed features of smart homes. These include face recognition, object recognition as well as voice and gesture control. All developed modules are published open-source on GitHub [5].

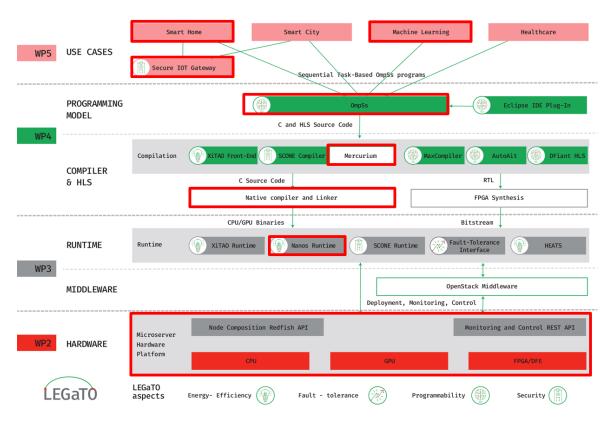

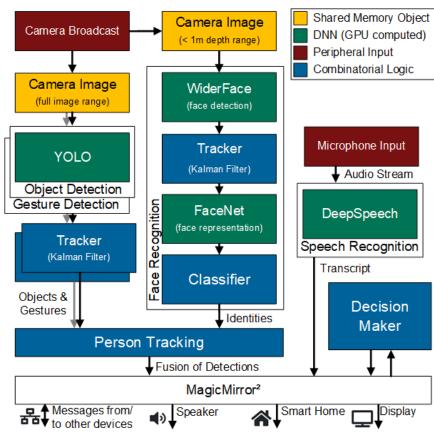

Figure 2: Used Tools in the smart home use case of the LEGaTO stack

Figure 2 shows the LEGaTO Tools used in this use-case. These are OmpSs with the Mercurium compiler and the Nanos environment and the hardware developed in this project. With this the energy efficiency is increased by factor 12 and compared with other implementation frameworks (MPI) the designer productivity was greatly increased.

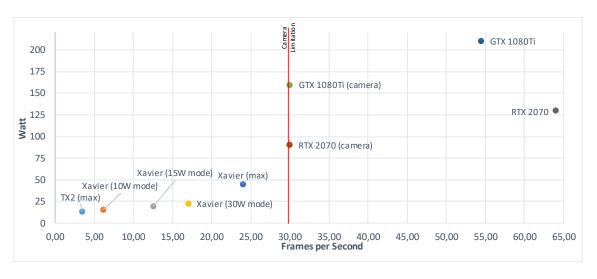

#### 3.1 Hardware evaluations and performance analysis with YOLO and Darknet

Multiple features of the smart mirror are based on the neural network called YOLO. It is a commonly used network for object detection. In the mirror application, two instances of this network recognize around 80 objects and 32 hand gestures. Therefore, it can be used as an indication for possible performance and hardware requirements. In this chapter, the performance on different hardware architectures is evaluated in regards to FPS and power consumption of running a single instant of YOLO for object detection. This is visualized in the following graph (see Figure 3) for NVidia TX2, Xavier embedded modules and GTX 1080Ti or RTX 2070 GPUs. In the prototype used Intel RealSense supports a maximum framerate of 30 FPS and is therefore marked by the red line. To measure the maximum performance on the GPUs, a video was used. The GTX 1080Ti runs one YOLO instance with 30 FPS and 160W power consumption with the Real Sense being the bottleneck. With a video around 54 FPS are reached, but the power consumption is increased to 210W. This is way too much performance and power consumption for an embedded hardware solution. The introduction of tensor cores on the RTX 2070 shows a possible solution for this. While bound by the RealSense 30 FPS about 90 W are reached. The maximum performance of one YOLO instance is 64 FPS and a power consumption of 128 W. If the tensor cores are not utilized, the maximum performance is reduced by 10 FPS, and the power consumption is increased by around 30 W. This demonstrates the potential of specialized hardware accelerators for neural networks. For possible embedded hardware solutions, NVidia TX2 modules are evaluated. With 13 W and 4 FPS the performance is not sufficient for the smart mirror use case. The NVidia Xavier module on the other hand shows a decent performance of 24 FPS at a power consumption of around 40 W in the max performance mode. The integrated tensor cores of these modules leveraged a possible embedded hardware solution.

Figure 3: FPS and Watt of Yolo running on TX2, Xavier, GTX 1080Ti and RTX 2070. The application is limited by the maximum output framerate (30 fps) of the Intel RealSense d435i (red line).

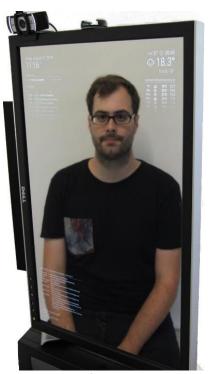

#### 3.2 Smart Mirror Prototype Hardware Setups

The smart mirror prototype is composed of a display with an applied semi-transparent mirror foil, a camera and a workstation. While first test was conducted with a small monitor and normal webcam, the later version of the demonstrator is utilizing an Intel RealSense and a big TV as a display. The RealSense was chosen for the featured depth images. These prototypes were also shown at several fairs to promote the LEGaTO project. At each workstation smart mirror prototypes, the overall application was distributed to two accessible GPUs, due to memory limitations on the GPU and to enhance the hardware utilization and user experience. On the embedded edge solution, complete processing parts are distributed over multiple microservers.

#### 3.2.1 The First Prototype

The workstation for the first prototype was composed of two GeForce GTX 1080Ti GPUs and an Intel i7-7700K processor with 32 GB of RAM. On this setup the first version of the demonstration was running with around 12 FPS in all detections simultaneously (face, gestures and objects) and a power consumption of 650W. After porting the limiting python scripts to C or C++ with CUDA optimizations, especially for Intel RealSense camera handler, the performance was enhanced to 16 FPS for the three detections. This can be traced back to a high CPU computation, for example, due to image scaling in python. Tracking and other additional features were not yet implemented in this setup. After the evaluation of the RTX 2070 the first setup was discontinued for the last period.

#### 3.2.2 The Second Prototype

The second prototype is composed of two GeForce RTX 2070 and an Intel ig-9900K with 32 GB of RAM. The introduction of Tensor Cores increased the performance to around 20 FPS for all three detections (face, gestures and object). At the same time, the power consumption was decreased to around 430W for the workstation. After additional optimization of the communication structure between the modules within the smart mirror application (number of image streams, partitioning) the performance was increased to 25 FPS for all detections. The latest features, like tracking, are added on this setup with minor performance reductions.

Figure 4: The first prototype setup

Figure 5: The second prototype setup

#### 3.2.3 Embedded Hardware Prototype

As shown in the evaluation of the Darknet framework on different GPU hardware, several NVIDIA Xavier modules should be very well suited to run the mirror. The first embedded hardware setup consists of two AGX Xavier modules, which are interconnected via a PCI Express bridge. Therefore, one module is configured as an endpoint device and a virtual Ethernet connection is established. The

Figure 6: Dual Nvidia Xavier prototype setup

bandwidth between those two modules is around 5 GBits/s with a roundtrip time of 1.5 ms. The Xavier modules are also one target architecture for the embedded edge server, but the performance of the virtual network within final edge server is expected to be much higher (around 40 GBits/s with a roundtrip time of < 1ms). Therefore, this setup can be seen as an intermediate step towards the final targeted hardware. The two modules have a combined maximum power consumption of 100W. The complete smart mirror application is ported to this setup, and the functionalities are partially optimized to utilise the second module. Hereby a performance of 16 FPS was achieved in the simultaneous execution of all detections at an energy consumption of 55W.

#### 3.3 Smart Mirror Software Optimization Progress

To improve the user experience and increase performance/energy efficiency, the data flow between the modules was changed, modules were reconstructed, and Kalman filters were introduced. These

changes have improved the performance and reduced power consumptions of the smart mirror demonstrator. Starting from about 12 FPS in each detection at a power consumption of 650W, the second iteration reaches 25 FPS at a power consumption of 430W on workstation hardware while all detections run simultaneously. Additional features have been implemented that increase usability and developer friendliness, such as a decision-maker who calls applications and displays content based on all information. Further optimizations and porting embedded hardware made the mirror demonstration running on a single Nvidia Xavier module. Due to the high number of neural networks and computations, this single device is capable of running everything

Figure 7: General structure of the smart mirror application

with 6 FPS by a power consumption of 42 W. The bottleneck in running on a single module is the GPU, which was fully utilized while core computation was free. With the help of OmpSs@Cluster, the computation of the object and gesture detection including the tracking is sourced out to the second Xavier. Thereby the GPU of the first module is greatly reduced by the cost of a slightly higher CPU utilization. This setup is running the full smart mirror with all detection at 16 FPS in average with a power consumption of 55W. With this setup the targeted performance in FPS per Watt is higher than the targeted result. The result of the final embedded edge server can be estimated to be similar, as the Xavier modules will also be used and consume the majority of the energy.

# 3.3.1 Module Reconstruction and Optimizations with C++ and Acceleration with CUDA

Several modules were first implemented in python because it is the common language for neural networks, and therefore a fast development could be done. An efficient image processing was neglected at first. After the initial evaluation, the following improvements were made.

- The main camera script, which prepares the RGB and the depth image, was ported to C++

and accelerations with CUDA were made. The CPU load has been reduced by 50% at the

cost of a slightly increased graphics card load, which is designed for such image processing.

This script provides the image to all other scripts via GStreamer appsink.

- To greatly reduce latency, the image showing all detections is created within the camera script and handed over to the Magic Mirror Framework. This workflow also has also removed the need to merge images of each module and removed the need to send back images from each module.

- Every neural network previously running on the smart mirror has needed a unique image resolution. In the first python version, this downscaling was also done by the CPU and before each inference and was thereby slow and inefficient. This was rewritten with GPU acceleration at a combined script. Some neural networks are also altered to use the same image resolution. Implementation via FPGA is desirable in the future.

- The darknet framework is also written in C and uses its own image format. The flow of scaling and converting is next to be combined and optimized.

- The first implementation of face recognition tried to identify each face in each image. This cost a lot of computation due to a large number of possible faces. By the introduction of the depth image this could already be reduced. By implementing tacking, faces do not have to be identified in every frame. In the current version, the identity is only checked once every second. This reduced the resource requirement enormously.

These changes together with the introduction of tensor cores have increased the performance from around 12 FPS at the first prototype to 25 FPS on the second prototype. They were also applied to the mirror running on a single Nvidia Xavier module but have shown only 6 FPS.

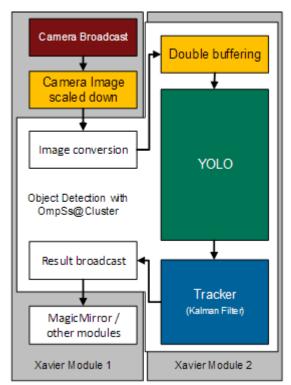

#### 3.3.2 Offloading of detections with Darknet using OmpSs@Cluster

Using OmpSs@Cluster, the computation of the object and gesture recognition is shifted from the system running the smart mirror application to an additional module. These modules are coupled via a network infrastructure and are using MPI as a backbone. In our case two Nvidia Xavier modules are coupled over a virtual Ethernet via PCI Express (see section 3.2.3). The general structure is shown in Figure 8. If only the object detection is examined, just the image conversion from the image

source into the format of the darknet library and the publication of the results is remaining on the first module. With the help of OmpSs@Cluster, the computation of the DNN and the tracking algorithm is entirely moved to the second module. All steps in this flow are separated into tasks, so all blocks can be executed in parallel, and the communication time is hidden. If only the execution of a detection alone is observed, the usage of the GPU is completely outsourced to the second Xavier module and the utilization of the CPU is increased a little bit. The performance in FPS remains identical to running it on a single node and is bounded by the throughput of the camera (30 FPS). Since the complete mirror application requires too much computing power from one module, the performance could be increased from 6 FPS to 16 FPS in all detections simultaneously by shifting the object and gesture recognition to the second Xavier module. This has moved the bottleneck from the GPU of the first module to the CPU cores of the first module. Further outsourcing of CPU computations will increase the performance even

Figure 8: Structure of the offloaded task for object/gesture recognition using OmpSs@Cluster

more. A slightly higher power consumption due to the communication overhead, next to the increased power consumption due to having two Xavier modules, has to be tolerated. For a more detailed description, see Deliverable 3.4 section 4.2.3.3.

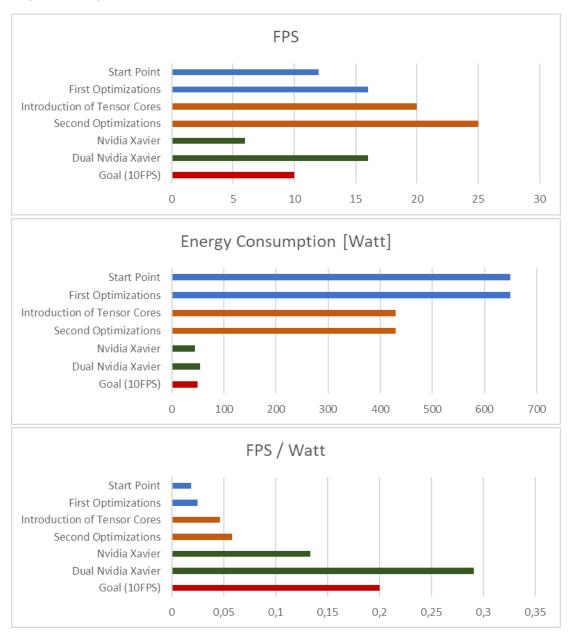

#### 3.4 Baseline Benchmark and Performance

As the baseline for the entire Smart Mirror, the total power consumption and the achieved frames per second in all detections simultaneously are considered. All results are shown in the following three graphs (see Figure 9). The colour of all three graphs represents the three different hardware setups and the goal. The first graph shows the achieved FPS, and the second graphs shows the average power consumption after each optimizations step. The third graph shows the combination of the previous graphs to express the performance. Here higher is better. The initial prototype achieved a performance of 12 frames with a power consumption of 650 W. This results in a value of around 0.018 FPS/W. After the first optimizations and translation from python to C++ with CUDA 16 FPS with a power consumption of 650W was achieved. This results in a value of around 0,024 FPS/W. With the second hardware prototype and the introduction of Tensor Cores, the performance was increased to 20 FPS with a reduced power consumption of 430 W, which corresponds to a value of around 0.046 FPS/W. After modification of the communication infrastructure and a finer granular subdivision, the performance was increased to 25 FPS with the same power consumption. Thereby around 0.058 FPS/W is achieved. The efficiency was thus increased by factor 3 due to the optimizations carried out so far. The optimized version was also runnable on a single Nvidia Xavier module. It achieved a performance of 6 FPS at a power consumption of 47 W. The Bottleneck, in this case, is the GPU, which is not capable of handling the high amount of DNNs. After offloading the computation of the object and gesture detection to the second Xavier module, the performance was increased to 16 FPS in all detection simultaneously with a power consumption of 55 W. This relates

in an efficiency of 0.29 FPS/W, which is higher than the goal of 0.2 FPS/W. If you compare the efficiency of the first prototype with the efficiency on the embedded prototype, the energy efficiency is increased by a factor of 12. This is possible by combining specialized hardware with the help of an adequate middleware.

Figure 9: FPS, Watt and FPS per Watt comparison between all performed optimization steps. Marked in blue the first, in orange the second and in green the embedded prototype. Red is the goal of 10 FPS by 50 Watt.

#### 3.5 Development of additional Features

In order to increase user-friendliness, additional functions are being developed. These include hand gesture recognition to control the mirror, Kalman filter and Hungarian algorithm for tracking detections, user behaviour prediction and recommendation. Therefore, a dataset of 32 hand gestures and a dataset of user interaction of the mirror is created.

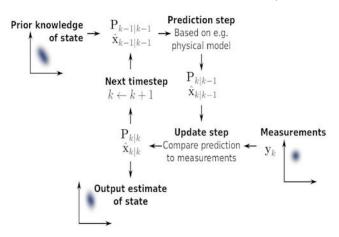

#### 3.5.1 Implementation of Tracking using Kalman Filters and Hungarian Algorithm

A very important feature is tracking the recognized faces, objects, and gestures. This allows many simplifications and increases usability. In the beginning, all decisions were based on findings only, but now the tracked detections are used to make decisions. Kalman Filters are used to predict the

next value for each detection. In our case, the input of these filters is the bounding boxes of each detection in each frame. With the Hungarian algorithm, the current detection and the predictions are cost-efficiently associated. After a small number of frames, an ID can be assigned for each detection. Thereby the detection is related to the previous detections. Predictions of the Kalman filter are also done and assumed to be valid even if no detection is visible for a short time. All different tracked detections are associated, and the

Figure 10: Workflow of Kalman filter and Hugarian algorithm for detection tracking

users can be tracked, even if they turn their face away, for example. The detection of persons is the key point for the whole mirror. For this approach, a Kalman filter is needed for each detection and cannot be shared. Many calculations can be done in parallel and are done so with the help of OmpSs parallel for pragma.

#### 3.5.2 Dataset of Hand Gestures for easy control

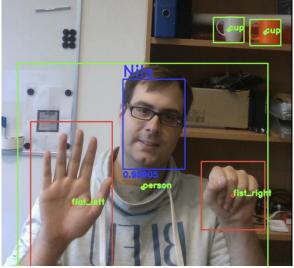

For an easy to use control of the smart mirror, hand gestures are used. No freely available data record has existed for this scope, so a custom data set had to be created. In order to train a DNN to recognize the desired gestures, a huge dataset is needed. The result consists of 32 hand gestures of 13 persons (examples for gestures are shown in Figure 12). We distinguish between left and right

hands and rotations are considered (e.g. thumbs up or down). This results in an amount of four hundred thousand images. Three persons are used for a test dataset, and nine people are in the training dataset. Further extensions are planned, and further special cases will be covered. Custom YOLO networks are trained with this dataset with the darknet framework. Some image augmentations are automatically done by this framework (e.g. colour shifts, scaling). The best results are achieved with yolov4-tiny with three YOLO layers. This runs on a NVidia Xavier with 30 FPS on the GPU by a utilization of 60%. The training reached a mean average precision of 92% by an intersection over the union threshold of o.5. This is an

Figure 11: Gestures are used to control the main menu. This example shows all outputs of the DNNs. Gesture with the center of the gestures in red

extraordinary result considering the size and texture of hand gestures. Due to data privacy reasons, the dataset cannot be made publicly available. A publication of the trained network is planned after further revision. For this purpose, further neural networks will be trained and compared. Due to the current world situation and difficulties in data acquisition, this was not possible within the scope of LEGaTO.

Figure 12: Example for the hand gestures in the dataset

#### 3.5.3 Behaviour Prediction of the User Interaction

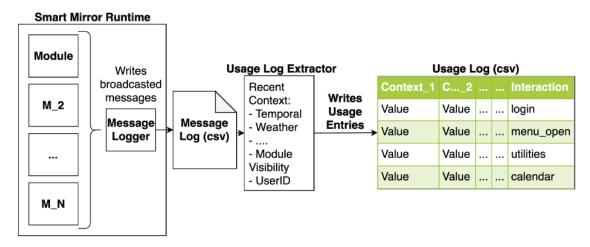

For a really intelligent mirror, a form of behaviour prediction is mandatory. Therefore, a large amount of usage data is needed. In order to gather this data, all messages broadcasted by the modules within the mirror are parsed and the status of the mirror is stored within a database. This database is continuously enlarged while running the smart mirror. Figure 13 shows the pipeline of this. Due to the current situation only, a small dataset could be gathered so far and interaction with multiple persons is also hardly represented. The first prototype is permanently exhibited on the corridor of our work rooms and trained test persons stand in front of it at regular intervals. This

Figure 13: Pipeline for status recording. These data entries consists of the status of the whole mirror and all information of the installed modules (e.g. weather forecast, mensa offering, visible objects).

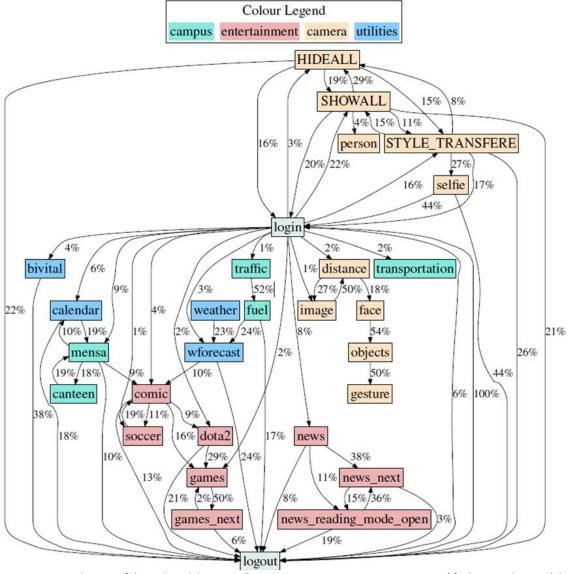

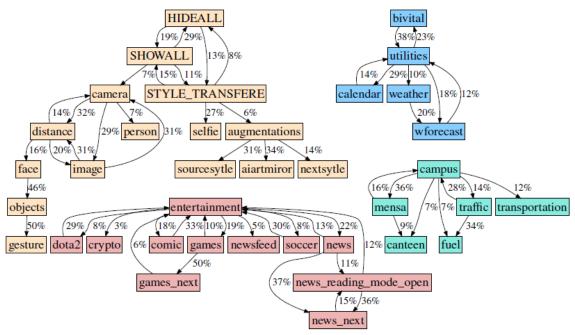

Figure 14: Visualisation of the gathered dataset. All points represent an action to open or modify the according modul. All actions can be grouped into 4 types. Campus, entertainment and utilities group the according modules and camera for the smart mirror

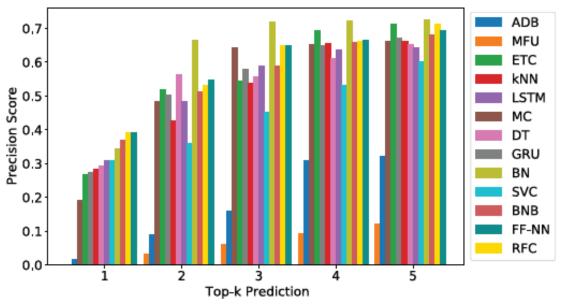

shows to be a good source of individual data sets. Sadly, public events, like fairs, were already virtual as we gathered data and due to distancing rules, data of presentations of the mirror are lacking. This must be considered in the following examinations and it explains why so far only the first examinations have taken place. The gathered dataset can be visualized with the graph in Figure 14. It shows the transition probabilities of all test users between the possible actions. The current status of the mirror offers a total of 33 different actions. The actions can be grouped into 4 different types. Campus, entertainment, and utilities are different categories of according applications (e.g. weather of utilities or cafeteria offering for campus). The category camera consists of all possible actions with regards to the camera of the mirror (e.g. show different detections or style transfer). The start point of all interaction with the mirror is the login state in the middle and all interactions stop with the logout of the user. Based on these data, different models were examined. The input for all subsequent models is the last 32 data entries of the database. Figure 15 shows the simple Markov chain representation of this graph. This is already a very good model to describe the problem of behaviour prediction for our case. Other investigated techniques of machine learning are: Adaptive Boosting classifier (ADB), Most Frequent Used (MFU), k-nearest neighbours (kNN),

Figure 15: Markov chain representation of the user interaction of the smart mirror

Long Short-Term Memory (LSTM), Markov chain (MC), Decision Tree classifier (DT), Gated Recurrent Units (GRU), Bayesian networks (BN), Bernoulli naive Bayes (BNB), Support Vector Machine Classifier (SVC), Feed Forward Neural Network (FF-NN) and Random Forest Classifier (RFC). The database is split into a training and a test part and all models are trained with the same partitions for a fair comparison. Interesting for behaviour prediction is not only the next interaction but the next k predictions (Top-k). This means, that in case of k=3 not only the next interaction is predicted, but the next three possible interactions. These can then be suggested to the user. Figure 16shows the precision for the different trained models. Because the data set is still quite small, these results are only conditionally meaningful and must be validated with more data. All except ADB and MFU and SVC have a similar good performance. Most promising seems to be a Bayesian networks with the highest score starting from k=2. In general, the performance of the prediction at top k=3 can be classified as 70%, which is a good result compared to literature values (from the area of

Figure 16: Results for the precision for the different trained models over different Top-k values

smartphones). Unfortunately, these cannot be compared directly with the values achieved here because the initial situation and implementation are too different. For a first recommendation system, the previously mentioned networks already show a sufficiently high accuracy as long as it is not necessary to differentiate for all users. If a user stands in front of the mirror doing nothing for a long time and the prediction shows a certain accuracy, a proposal can be made. Here the behaviour of other users can also support. A further step can be to detect anomalies if the behaviour of one user is in total contrast to the user's normal behaviour.

# 4 Smart City

In many urban areas, air quality and associated impacts on public health are matters of growing concern. The emission and dispersion of critical pollutants ( $PM_x$ ,  $NO_2$  and ground-level  $O_3$ ) correlate with cancer, asthma, cardiorespiratory problems, brain development in children and reduction of life expectancy in general [6]. As a consequence, air quality monitoring networks and modelling forecasting systems are critical to increase awareness and, ultimately, to assist decision-makers on the adoption of measures to protect public health.

Figure 17: Used Tools in the smart city use case of the LEGaTO stack

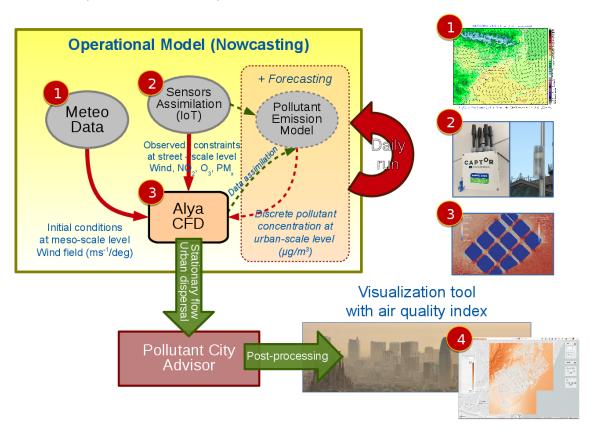

The Smart City use case is composed of four different components that, individually, meet a specific project objective and, in combination, allows the development of an operational air quality modelling system at street-level resolution based on CFD. Figure 18 shows the key components of the air quality modelling system. Most of the individual components have already been developed within other research projects. In this operational workflow, different inputs are required by the CFD model to simulate urban-scale winds:

- Meteo data: CFD models require initial boundary conditions to confine the physical

problem into a finite computational domain (e.g., a city mesh). These boundary conditions

set the inputs of our CFD simulation, defining how the fluid, or wind in our case, enters

(inlet) or leaves (outlet) the domain. In other words, boundary conditions connect the

region of interest (our urban area) with its surroundings.

- Sensor assimilation: In order to model and forecast urban-scale pollutant dispersion, it is

not only necessary to dispose of high-resolution near-surface wind fields, but also to

characterize the sources of pollutants at street-level (mainly derived from vehicle

combustion) through sensors or emission inventories

- CFD-based wind and pollutant dispersal modelling: Within the Smart City use case, the CFD-based simulator is the main core of the whole application. To this end, an urban-scale wind forecasting system was developed, based on coupling the meso-scale WRF model (a numerical weather prediction system) [7], with BSC's Alya modelling system [8], a CFD-based simulator. In order to simulate the air flow through the urban-scale morphologies (buildings), the CFD model solves the incompressible Navier-Stokes equations on a computational mesh that represents the city geometry. However, due to its physical complexity, the use of CFD techniques requires massive computing resources.

- Data gathering and streaming: After the simulation, data is collected directly from the CFD model and the environmental network. Pollutant data is post-processed and published using an Open Data format in a BSC repository. The post-processing may require large amount of memory resources to be interpolated and stored in databases depending upon the mesh size and refinement. Finally, the data provided might be used by visualization and analysis tools for their study.

Figure 18: Conceptual sketch of the urban-scale air quality forecast system

On top of this model, the most critical components have been chosen to take advantage of the LEGaTO platform. Actually, within this workflow, the Alya CFD-based simulator is the main compute-intensive component and the one that takes longer to run, and therefore some of its kernels are the main target to be ported to the LEGaTO stack. The source code can be found under https://github.com/legato-project/FinalSoftwareStack

This use case aims at demonstrating that monitoring of urban air quality through CFD simulations is feasible for short term forecasts (also known as nowcasting) in an operational workflow built on top the LEGaTO stack.

#### 4.1 Metrics & Optimization Goals

Due to the operational context of the Smart City use case, the air quality model must be constantly executed every update period with new input data from pollution sensors and the meteorological agency. The update period can be so small, between 30 minutes and 1 hour, that it can be critical for running the whole simulation. In this scenario, the LEGaTO stack is pivotal, both in terms of leveraging the processing capabilities to shorten simulation times and improving the energy-efficiency of a highly-demanding urban-scale air quality modelling system. In order to evaluate the LEGaTO implementation, two main metrics must be gathered:

- Use case performance: elapsed time per CFD simulation (*metric* 1).

- Energy-efficiency: Joules per CFD simulation and FLOPs/watt (metric 2).

Using the previous two metrics, the following LEGaTO optimization goals will be evaluated for this use case:

- Allow complex urban area simulations (metric 1): leverage total execution time objective (10x faster).

- Increase update frequencies in the operational context (*metric 2*): one order of magnitude in energy-efficient objective (10x energy savings).

- Improve FPGA designer productivity: ease the porting of compute-intensive kernels to FPGAs devices using OmpSs model.

- Increase the MTBF factor: support fault tolerance by means of agnostic FPGA task checkpointing, allowing task replication and reduction of failures during simulations (5x increase).

#### 4.2 Baseline Benchmark

Once that the functionality of the LEGaTO version is checked, a baseline test case must be used to benchmark the Smart City use case. This test set will be used to evaluate the optimization goals of the LEGaTO implementation with respect to the original code using the agreed metrics. The test set was run on MareNostrum IV supercomputer, and the most important metrics were obtained as a reference for the baseline. These metrics will be used in future analysis to evaluate the improvement of the LEGaTO implementation.

The baseline evaluation is performed using a pure-MPI Alya CFD version running the Smart City application. Then, we will evaluate the application by applying the LEGaTO optimizations mentioned above. These will include OmpSs taskification to express efficient parallel execution of the application, using single or mixed-precision floating point with minimal loss of quality, and vectorization for efficient execution on accelerators.

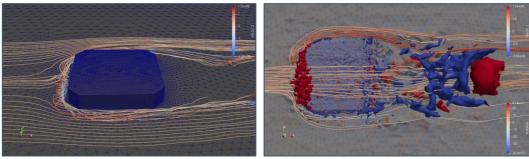

The test set used for the baseline comparison is composed of two tests, a minimal mesh and a full-size mesh:

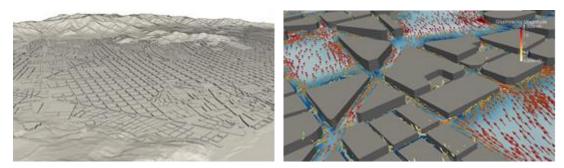

• Test 1: proof of concept mesh with a single square building block of 22 meters height and 150 meters long on each side (see Figure 19). The whole urban-area mesh is composed of

LEGATO D5.3 Version 1.1 23 / 81

- almost 1 million tetrahedral elements, with a higher element refinement on the boundary layers of the building and on its leeward wall (downwind side of the building).

- Test 2: full-sized mesh of Barcelona city geometry of 500 meters high (see Figure 20). The whole urban-area mesh is composed of 80 million tetrahedral elements, each element with a minimum resolution (length of the element faces) of 15 meters at surface level (streets and building walls).

Figure 19: Mesh with a single building block

Figure 20: Mesh with a full-sized urban mesh from Barcelona city

As initial condition for the simulations, a west-component (180 degrees) logarithmic wind field profile (10 m/s $^{-1}$  on the top boundary) is used.

Each MareNostrum IV node in our testbed platform is composed of 2 sockets with Intel Xeon 8160 processors with 24 cores each. They run at a frequency of 2.1 GHz and have 96 GB of main memory. One single node was used for test 1 (48 MPI tasks) and 10 nodes were used for test 2 (480 MPI tasks). Using this configuration, the Alya's CFD model was run in a pure-MPI parallel way over 100 timesteps for both tests. Different metrics were taken from the job execution for future comparisons with the FPGA versions.

On the other hand, we also run some initial tests on the AXIOM board platform. This is an ARM64 bit architecture with a Xilinx FPGA accelerator [9]. However, given the memory constraints on this platform, only the ARM64 processor was feasible to be used with the single building block test (*test* 1). The results obtained on both platforms for metrics 1 and 2 were:

| Baseline metrics | Explicit<br>momentum | SpMV    | Whole simulation |

|------------------|----------------------|---------|------------------|

| Elapsed time     | 12.63 s              | 2.08 \$ | 28.75 s          |

| Energy consumption      | - | - | 9741 Joules<br>(2.7 Wh → ~0.3 Wh in the FPGA) |

|-------------------------|---|---|-----------------------------------------------|

| Performance per<br>Watt | - | - | 273 MFLOPs/Watt<br>92.5 GFLOPs (per node)     |

Table 2: Metrics for test 1 on MN4 using 48 MPI tasks

| Baseline metrics        | Explicit<br>momentum | SpMV | Whole simulation                             |

|-------------------------|----------------------|------|----------------------------------------------|

| Elapsed time            | osed time -          |      | 29800 s                                      |

| Energy consumption      | -                    | -    | 195190 Joules<br>(54.2Wh)                    |

| Performance per<br>Watt | -                    | -    | 12.96 MFLOPs/Watt<br>84.92 MFLOPs (per node) |

Table 3: Metrics for test 1 on AXIOM board using 4 OpenMP threads

| Base line metrics       | Explicit<br>momentum | SpMV    | Whole simulation                                              |

|-------------------------|----------------------|---------|---------------------------------------------------------------|

| Elapsed time 654.9 s    |                      | 268.7 s | 1505.45 s                                                     |

| Energy consumption      | -                    | -       | $4733167$ Joules (1.3 KWh $\rightarrow$ ~0.1 KWh in the FPGA) |

| Performance per<br>Watt | -                    | -       | 175 MFLOPs/Watt<br>55.2 GFLOPs (per node)                     |

Table 4: Metrics for test 2 on MN4 using 480 MPI tasks

## 4.3 Development Status & Optimization Path

Within the Smart City use case, the CFD-based simulator is the main core of the whole application. To this end, an urban-scale wind forecasting system was developed, based on coupling the meso-scale WRF model with BSC's Alya modelling system. On top of this model, the most compute-intensive kernels are being ported to take advantage of the LEGaTO platform. Two main hotspots have been identified as targets:

- Explicit momentum solver: long numerical code where the submatrix for each element in the mesh is computed and assembled in the global system. This is the main optimization target due to their computational cost (~60% of the global time). (kernel 1)

- Sparse Matrix Vector operation (SpMV): Sparse L2 BLAS operation used in both explicit momentum (just once per time-step) and implicit pressure solver (iteratively until

convergence criteria is reached). Due to its relative computational cost (~10-15% of the execution time) this operation has been also considered to be ported. (kernel 2)

The porting of those two kernels to the LEGaTO stack requires at least two operations: the full rewrite of the Fortrango kernel codes to C language, and the kernel taskification with OmpSs programming model. Note that both algorithms are dominated by the indirect memory accesses due to the unstructured mesh connectivity.

The first step consisted in developing a fully ported of both kernels to C and has been taskified with OmpSs. The kernel has successfully been compiled and run on Intel and ARM64 platforms (Intel Xeon Platinum 8160, Cavium ThunderX2 64-bit ARMv8 [10] and AXIOM board [9]), where the baseline test-case for the Smart City use case was executed to validate the correctness. These kernels were also annotated with OmpSs@FPGA directives in order to run on the Xilinx Zynq Ultrascale+ FPGA on the AXIOM board. However, the existing memory on that device was not sufficient to execute the test-case. Its 4GB of memory were not enough to load the mesh, allocate Alya physical variables, use the OmpSs backend (libnanos), and allocate the required buffers to transfer data back and forth to the FPGA processor. As a workaround and for future testing, the development has been moved to a PCle Alphadata FPGA board [11] which incorporates more memory.

The second step consisted in developing an optimal implementation of the SpMV on the FPGA board. The main reason to start with kernel 2 is that improvements developed on this kernel would easily be applied on kernel 1, which is more complex to develop. On the SpMV, the main performance issue to consider is the storage format of the sparse matrix. The sparsity pattern of the matrices arisen from Alya is highly irregular since it represents the connections from the cells of an unstructured mesh. The number of non-zero elements per row depends on the geometrical shape of the cells, and for tetrahedral meshes is 5 for almost all the cells. The rows that represent the connections with boundary conditions have less non-zero elements, zero padding is applied on those rows to introduce regularity. CSR is the most common storage format used on sparse matrices, however in the Smart City use case the optimal storage format is the sliced ELLPACK [12].

Three different implementations using FPGA were compared with the CPU version on the PCIe Alphadata FPGA board: i) the naïve implementation using the same ELLPACK format than the CPU ii) an optimized CSR found in the literature [13], and finally, iii) a tuned ELLPACK format that aims at reusing the data by implementing a cache like structure that optimizes the reading of multiplying vector.

For testing the implementations, a set of matrices arisen from Alya with sizes ranging from 50,000 rows up to 800,000 rows was utilized. The optimized CSR has the limitation that the resulting vector needs to be fully loaded into local memory, and therefore, the matrix size is limited by the architecture specifications. The execution times are shown in Table 5.

|               | 50,000 | 100,000 | 200,000 | 400,00 | 800,000 |

|---------------|--------|---------|---------|--------|---------|

| NAÏVE         | 0.138  | 0.277   | 0.545   | 1.183  | 2.335   |

| CSR OPTIMIZED | 0.112  | 0.221   | 0.425   | 0.903  | 1.758   |

| ELLPACK       | 0.017  | 0.025   | 0.036   | 0.075  | 0.142   |

| CACHED        |        |         |         |        |         |

| CPU           | 0.001  | 0.003   | 0.005   | 0.012  | 0.023   |

Table 5: Execution time in seconds for the SpMV using different implementations on the FPGA

The results show that the optimized FPGA outperforms in up 16 and 12 times the naïve implementation and the optimized CSR, respectively. However, in its best case runs 6 times slower than the CPU version. The unstructured memory accesses are difficult to map on the FPGA, needing of extra logic on the die that reduces the possibility of exploiting the parallelism. These results lead to the decision of changing the LEGaTO component to the NVIDIA Xavier boards as explained in the next section.

#### 4.4 Final numerical results

The LEGaTO component utilized for the numerical results consisted in two NVIDIA Xavier boards connected through a PCIe link developed at Bielefeld. One of the characteristics of the Xavier boards is that the maximum energy consumption can be altered by changing the frequency, power budget or the number of cores available. Each board has up to six different setups, so called energy modes. In our case, the most representative modes are:

- Mode o: Full computing capability, at 2265 MHz frequency, and no power budget (8 cores and GPU available)

- Mode 3: Full computing capability, at 1200 MHz frequency, and a power budget of 30W (8 cores and GPU available)

As a baseline we have considered the execution using one MareNostrum4 node. The node is composed of two Intel Xeon Platinum 8160 summing up 48 CPU cores.

Alya parallelization strategy is based on a geometrical domain decomposition. A partition of N subdomains requires of launching N+1 MPI processes. The process with rank o coordinates the work, while for each of the remaining N processes (workers) a unique subdomain is assigned. Point-to-point MPI communications transfer the data between adjacent subdomains, while collective communications involve all the processes. CUDA is used to engage the Xavier board GPU. An overlapping strategy is utilized to hide part of the overhead of performing MPI+CUDA communications. Moreover, all the MPI processes (workers) launch CUDA kernels to the same GPU.

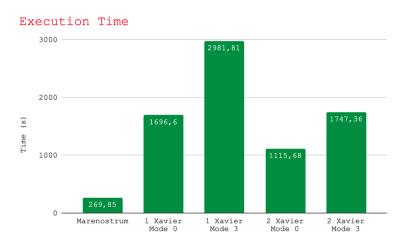

The execution time of the time integration of 1000 steps has been considered. Note that the preprocessing stages are not measure here since in a real simulation its costs become negligible compared with the millions of time integration steps needed. The results are show on Figure 21.

Figure 21: Total execution time of Alya test case for different configurations

The results show that the faster execution utilizing a single Xavier Board is obtained when the energy mode with maximum consumption is activated (mode o). This is also true when engaging

both boards of the prototype, however the performance doesn't scale linearly. Only a 50% of acceleration is attained by adding an extra Xavier board in the calculation. The performance degradation can be explained by the overhead introduced by the PCIe interconnection between the cards when point-to-point or collective communications are needed.

In addition, a MareNostrum4 node (48 cores) runs 6.3 times faster than a single Xavier board (8 cores+GPU) at its maximum energy mode.

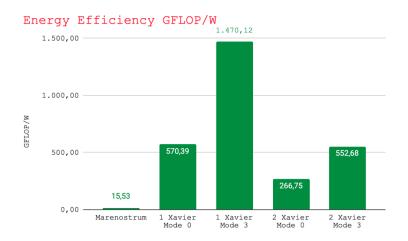

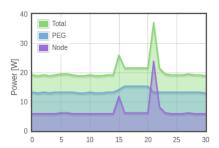

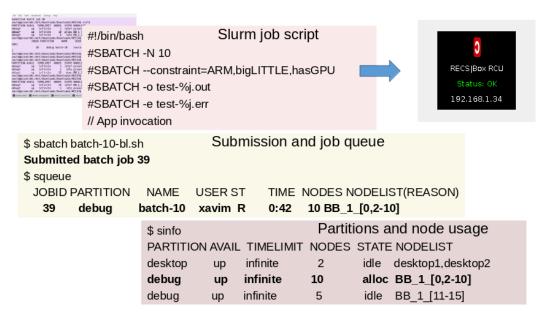

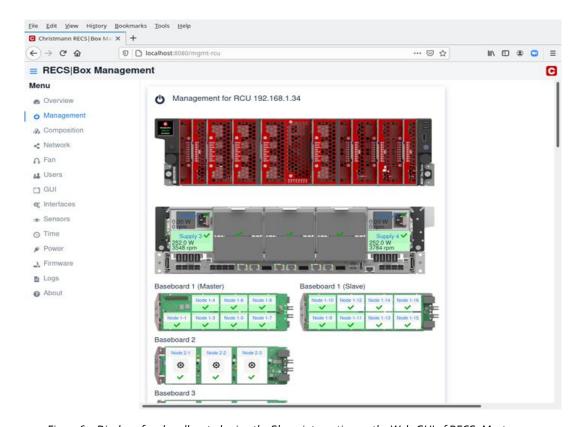

Despite the slower results of the prototypes, a more interesting perspective can be obtained by analysing the power consumption on each platform. In MareNostrum4, jobs are launched using the Slurm Workload Manager [14]. While running, Slurm collects performance and power consumption information that we gather and analyse. For the Xavier prototypes, the tegrastats tool [15] provided by NVIDIA reported such information. In both cases, the full power consumption of the node was considered. The results presented in FLOP per watt are depicted in Figure 22.

Figure 22: Energy efficiency in GFLOP/W for different setups

The energy measurements show that one Xavier board in mode o is 35 times more energy efficient than the Marenostrum4 node. Moreover, if the Xavier mode is utilized in mode 3, the energy efficiency achieved is 95 times at the cost of 11x slowdown. When using 2 Xavier boards, the speedup obtained is only 1.7x (due to the overhead of communications), and as a result, the performance and energy - efficiency do not get benefits. One may consider to use the 2 Xavier boards in mode o, to get better performance at the expense of being less energy efficient

The current configuration of the Bielefeld Xavier prototype allows engaging only up to two Xavier nodes. A rough estimation of the performance using more nodes is possible by measuring solver calculations and communications times separately for different workloads.

The time of calculations are measured locally using one Xavier node for matrices ranging from 50,000 to 1,600,000 rows. Note that by doing this we are assuming an optimal distribution of workload among the nodes. The next step consists in estimating the communication costs only using 2 nodes. For this task, we have measured the communication between two nodes using different message sizes. The main assumption is that the slowdown in performance when passing from 1 to 2 nodes is going to be just scaled by the message size when passing from 2 to 4 nodes. The calculation and communications times are shown in Table 6.

| Nodes          | 1         | 2       | 4       | 8       | 16      | 32     |

|----------------|-----------|---------|---------|---------|---------|--------|

| Local workload | 1,600,000 | 800,000 | 400,000 | 200,000 | 100,000 | 50,000 |

| Calculations   | 5.64      | 2.18    | 1.07    | 0.42    | 0.29    | 0.16   |

| Communications | 0.03      | 0.18    | 0.78    | 1.03    | 4.03    | 12.66  |

| Total Time     | 5.67      | 2.35    | 1.85    | 1.45    | 4.32    | 12.83  |

Table 6: Execution time in seconds of the calculations and communications of Alya's solver for different workloads

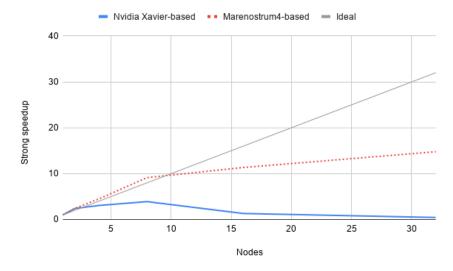

The final scalability is obtained by adding the calculation and communications costs. The estimation of the scalability of the solver using up to 32 nodes is depicted in blue on Figure 23. It is clear that the communication cost becomes a bottleneck when the workload per node decreases.

A more optimistic approximation can be done by assuming that the network would behave as in Marenostrum4. For that matter, the communication using two nodes was measured, and then, scaled according to numerical results obtained on Marenostrum4. The dotted on the figure represents the MareNostrum4-based estimation. Note that a better network would improve the performance on the prototypes, and therefore, it would increase the gap in terms of energy efficiency between both configurations.

Figure 23: Estimation of the scalability of Alya

#### 4.5 A low energy-consumption Alya-oriented cluster

Alya is one of the twelve simulation codes of the Unified European Applications Benchmark Suite (UEABS), and therefore takes part in many scientific projects that result in using a large part of the PRACE infrastructure. On Marenostrum4, Alya-based simulations are one of the main applications that exploit the supercomputer. Over the last year, the majority (~60%) of Alya-based simulations engaged an average of 50 computing nodes (2,400 CPU-cores) on MareNostrum4. Consequently, it would make sense to create an infrastructure oriented to solve simulations on that size range, since it would have the largest impact on Marenostrum4 power consumption.

An estimation of the size of the new infrastructure can be obtained considering the optimistic scalability estimations. For this purpose, three assumptions are needed:

- 1. the simulation results on the new infrastructure should be attained on a similar time frame

- 2. a node of Marenostrum4 is 6.3 times faster than a Nvidia Xavier node (see Figure 20)

- 3. up to 9.3 times of acceleration would be obtained by using 8 Xavier nodes (see Figure 22)

The conclusion is that the new low-energy consumption cluster should be composed of 400 Nvidia Xavier nodes that would deliver the same execution time on the average usage of Alya, than the usual 50 Marenostrum4 nodes.

The ratio of power consumption between a node of Marenostrum4 and a Xavier node is approximately 35 times when running an Alya use case. Then, the new cluster that would need 8 times more nodes would consume approximately 4.4 times less energy than Marenostrum4. Since the new cluster would be used on 60% of Alya executions, the other 40% would still consume the same. Therefore, the overall power consumption of Alya would be reduced by 47%.

#### 4.6 Increase robustness for Alya at large scale

The smart city use case sometimes requires runs with very high resolution and long timelines. It is not surprising for some of those runs to take hundreds of hours of execution, spanning over several weeks in multiple runs of 24 to 48 hours. In addition, these simulations usually run on thousands of processes, consuming hundreds of thousands of CPU hours.

Supercomputers at the petaflop scale with thousands of computing nodes, such as the Marenostrum4 supercomputer at the BSC, usually observe around three node failures per day, translating into a mean time between failures (MTBF) of about 6 to 8 hours. At this scale, any failure immediately translates into huge energy waste. Therefore, we apply checkpoint/restart (see chapters 5.1 and 5.2 of Deliverable 3.3 [16]), to substantially decrease the amount of re-computation required upon a failure. However, checkpointing had not been applied to the GPU version of Alya previously. It is not easy to checkpointing heterogeneous applications as one must work with multiple memory devices, the host and the device memory.

In LEGaTO, we have created a tool capable of checkpointing heterogeneous applications running on GPU clusters, such as Alya. Moreover, our tool leverages multiple storage systems implementing multilevel checkpointing, and we parallelize device-to-host data streams, with writing into reliable storage (i.e., SSDs, PFS). In this way, we have not only enabled fault tolerance for heterogeneous applications but also decrease the checkpoint and recovery time by up to 15.23X and 5.21X, respectively. Furthermore, for the same amount of waste, i.e., 15%, our checkpointing technique can sustain execution in systems with 6.3 times smaller MTBF [17].

LEGaTO D5.3 Version 1.1 30 / 81

# 5 Infection Research

Recently, biomarkers are used widely in medical research to detect a disease early, for diagnosis, in making prognostic or risk assessments, which nowadays plays an important role in modern clinical and preventive medicine. By modern technologies like microarrays, next generation sequencing, and mass spectrometry, researchers can measure many biomarkers that may exceed ten thousands [18] [19] [20]. With this development comes the challenge to find biomarkers to detect the risk to have a disease or diagnose it with high confidence.

To avoid wasting time and money, researchers do pilot studies with a small number of observations as necessary first step for biomarker discovery. Because of the small number of cases and the large number of biomarker candidates, any result might be caused by random effects and statistical significance cannot be proven. For that, researchers try to reduce the number of biomarkers and extract the most informative ones from these pilot studies to then increase the sample size and achieve an adequate statistical power.

#### 5.1 Description of the accelerated biomarker discovery workflow

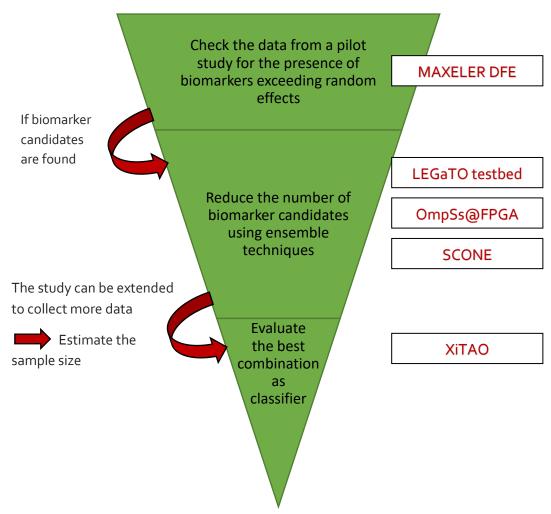

Figure 24: Accelerated biomarker discovery workflow

LEGATO D5.3 Version 1.1 31 / 81

Figure 25: Healthcare Toolchain

The discovery of biomarkers, from the pilot study to the biomarker that can be used in practice, involves several different steps of data analysis, as shown in Figure 24. In order to accelerate the workflow described in detail below, we have used several components of the LEGaTO toolchain, see Figure 25.

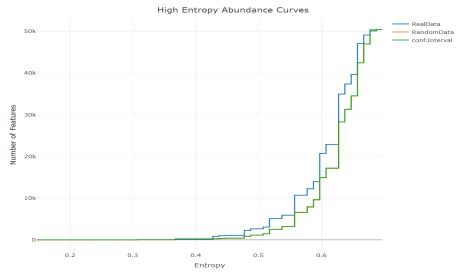

In a first step, we check the data for the presence of biomarkers that have an association with an outcome exceeding the pure random effect. Our new HiPerMab curve method (to be published soon) shows how many biomarker candidates in the real data set exceed a specific value of entropy (a performance measurement) compared to a random data set and a confidence interval, see Figure 26. To measure the probability of how many biomarkers exceed a specific value of entropy, simulations have to be done.

Figure 26: The number of biomarkers with a performance value that does not superpass a specific value of entropy

In cooperation with Maxeler and their MaxCompiler, the computing time for the simulations has been reduced dramatically by accelerating key parts of the computation with Maxeler DFEs. As a first step, the application was profiled for its most computationally intensive components. These ones naturally represent the best opportunity for application speed-up. Due to the close link between efficient processing in terms of speed and energy on DFEs, successful application speed-up by offloading computation-intensive parts to DFEs also typically leads to significant energy reductions. In this case, the cut index function which is part of the R package "discretization" was chosen for DFE offloading and acceleration. This process meant the cut index functionality was reimplemented in Maxeler's MaxJ language and compiled to a state-of-the-art MAX5 DFE card with MaxCompiler. In order to facilitate the integration of the DFE accelerator functionality into the original R application, a C++ interface layer was created in order to call the Maxeler SliC API [21].

To reduce the number of biomarkers (also called features), we extract the most informative ones simply by ranking them according to AUC, entropy, sensitivity, specificity or other metrics. This approach of feature selection by filtering is relatively fast but does not take relationships between biomarkers and biomarker combinations into account.

Along with the advancement of high-throughput technologies that allow measuring the whole or large parts of the genome, transcriptome, proteome or metabolome, came a strong hope to find a single biomarker for each disease or state of a disease to be diagnosed with very high certainty. However, this dream did not come true, and it seems to be unrealistic from today's point of view. Biological systems are probably too complex for simple single-cause single-effect associations. Nevertheless, there are biomarker candidates that show a high correlation with specific diseases but are not reliable enough to function as predictors for the presence of a specific disease alone. Instead of relying on a single biomarker, the idea is to combine biomarkers that are not good enough for the diagnosis of a specific alone but can jointly provide a diagnosis with high certainty. Therefore, we additionally apply embedded feature selection with tree-based methods (random forests and gradient boosted decision trees), including the calculation of the robustness of the feature selection. Building thousands of models and finding the best set of hyperparameters is computationally expensive. This step of the workflow is accelerated based on the results of the accelerated HiPerMab curve method from the first step. In addition, we use a fast C++ implementation with Python bindings (lightGBM [22]) and a hyperparameter optimization software (optuna [23]), which generally speeds up the selection of hyperparameters. This optimization was developed on the LEGaTO testbed in Bielefeld and was made possible by the technical support provided there.

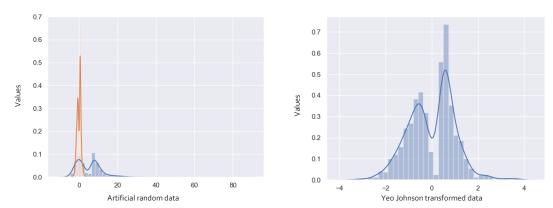

To verify results that are not very robust, we want to use ensemble techniques. That is why we have added another new approach to the workflow. In this further algorithm, we do not predict the class directly from the training data. Instead, we predict every biomarker candidate by LASSO regression [24]. From the importance of the included class label for the prediction and the regression error, we calculate a weight for this specific biomarker candidate. We assume that the higher the weight, the more relevant the biomarker candidate is. Due to timing reasons explained in the deliverable 5.2 and to use more diverse algorithms we switched the regression method from lightGBM ([15] a tree-based method) to LASSO regression [17]. The LASSO regression has only a single hyperparameter that can be determined quickly. In addition, the LASSO algorithm is less complex and faster. As a pre-processing step for the LASSO regression, the skewed biological data must be scaled and transformed into a distribution close to a normal distribution. An example with randomly generated artificial data is shown in Figure 27. For this necessary transformation, we use the Yeo Johnson Transformation [25].

Figure 27: Skewed random data versus the transformed data

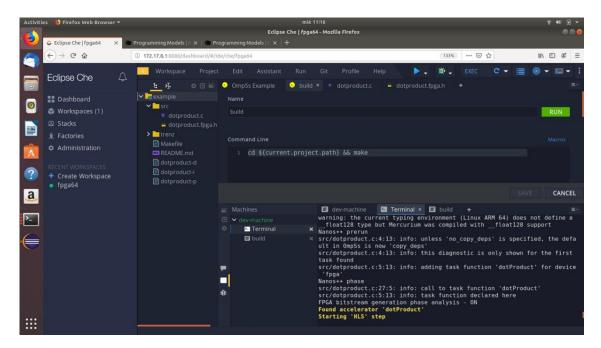

To accelerate this time-consuming transformation for large data sets we use OmpSs@FPGA. The implementation of the transformation was done in C and subsequently modified with corresponding OmpSs@FPGA and HLS instructions so that the time-consuming part of the program could be processed in the Programmable Logic of Zynq-7020 ARM/FPGA SoC Development Board. The transformation of an input vector was processed in a hardware pipeline so that the next iteration starts before the previous iteration is finished.

At no point the use of a hardware description language (HDL) or knowledge about it was necessary, so OmpSs@FPGA fulfils the approach of a high-level synthesis very well and is a proof for increased designed productivity compared to HDL languages. Another advantage is the common address space of the Programmable Logic (PL) and the Processing System (PS). This allows a realization of the task like on a normal PC.

The BSC provides a boot medium for the supported systems, on which operating system, runtime environment and libraries are installed. The BSC relies on the Docker technology for the distribution of the software for the OmpSs@FPGA project. By providing the appropriate image, the developer can download the desired OmpSs version for the target system as an image and start it in a container. In this container, an operating system with the necessary toolchain is available and can be used immediately. Only the "FPGA specific vendor tools" have to be inserted into the path of the started container. In the case of the Zedboard, which has a Z-7020 from Xilinx as FPGA, it was the Vivado Design Suite from Xilinx.

This type of acceleration could also be applied in other similar applications that transform data for biomarker discovery and be added to the biomarker discovery workflow.

Furthermore, we integrated the part using the LASSO regression with SCONE to test and show the possibility of secure data processing even in the cloud. Sensitive medical data can be handled according to data security aspects.

Combining the information of the different approaches explained above, we select a subset of biomarker candidates. We then estimate the sample size for extended studies in order to achieve adequate statistical power. After collecting enough data, we repeat the biomarker selection process and evaluate the best combination of biomarkers using Random Forests.

In our previous version of this algorithm, we selected the 18 most promising biomarker candidates from a data set with 66 samples and calculated every possible combination within this selection. From a statistical point of view, however, the number of biomarkers in the classifier should not exceed 10% of the sample size, and from a medical point of view, researchers prefer to have as few biomarkers in the model as possible. For this purpose, we optimized the code in a first step by

reducing the number of biomarker candidates contained in the classifier to a maximum of 6. We have parallelized the adapted code for the new baseline measurements. In order to really achieve a significant acceleration, we have implemented the complete algorithm again in C++ and accelerated this implementation with XiTAO (c.f. section 8.1). We chose XiTAO because it is very simple to integrate into C++ code and the program can be run on any computer. Depending on the number of available cores, the acceleration can easily be adapted to the respective hardware environment. This part of the software can be reused without any special hardware requirements.

The optimised software used in the Infection Research use case can be requested via Prof. Dr. Frank Klawonn <frank.klawonn@helmholtz-hzi.de>, who is leading this use case at the Helmholtz Centre for Infection Research.

#### 5.2 Metrics & Optimization Goals

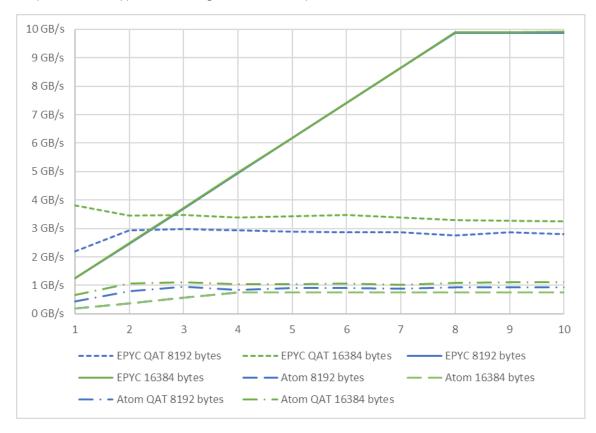

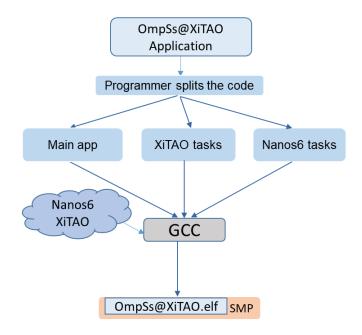

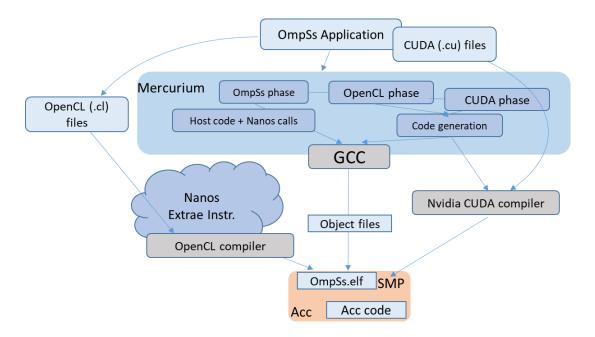

We could reach our main optimization goal to achieve a significant speedup in several parts of our biomarker discovery workflow. This enables us now to handle larger data sets (especially in terms of biomarker candidates). The number of biomarkers and the size of the data sets we are able to handle is crucial for our future projects. We are part of the project consortium i.Vacc (paving the way towards individualized vaccination) [26]. The project started in 2020 funded with one million Euro within the framework "Big data in the future life sciences" of the Lower Saxony Ministry for Science and Culture in Germany [27]. In contrast to our other projects where we usually handle data from one so-called omics fields (metabolomics, proteomics, transcriptomics, genomics), we will look jointly at different types of omics, increasing the number of biomarker candidates drastically. Analysing data from three or four different omics fields jointly does not mean that we have to apply our algorithms three or four times but the size of the biomarker candidate data set increases by factor of three or four. Our goal is therefore to work with data sets at least three times as large as the ones we could handle before. This means we want to extend the number of biomarker candidates to >50,000 and the sample size to >100. With the optimizations achieved in the LEGaTO project, these calculations are now possible.