News & press releases

State Machine and Loop Abstraction in DFiant

DFiant is a dataflow hardware description language (HDL) that participates in the LEGaTO stack to allow users better control over the generated FPGA hardware for their applications. DFiant is a novel HDL that provides unique abstraction beyond the classic register-transfer level (RTL). This abstraction disconnects the application from target-bound hardware description and enables automatic pipelining. Nonetheless, DFiant is not a classic high-level synthesis (HLS) abstraction either, since it does not have sequential semantics that can result in either parallel or sequential circuitry.

Sequential execution in software is equivalent to a finite state machine (FSM) in hardware design. In typical HDLs, parallel hardware design is trivial, but FSMs are often described as a combination of a state variable and a case statement that controls the state transformation according the input and current state. These FSMs can easily become too verbose and complicated. Furthermore, it is difficult to share commonalities between such FSM descriptions (cannot share a part of a case statement). We decided to take a different approach in DFiant to resolve these issues.

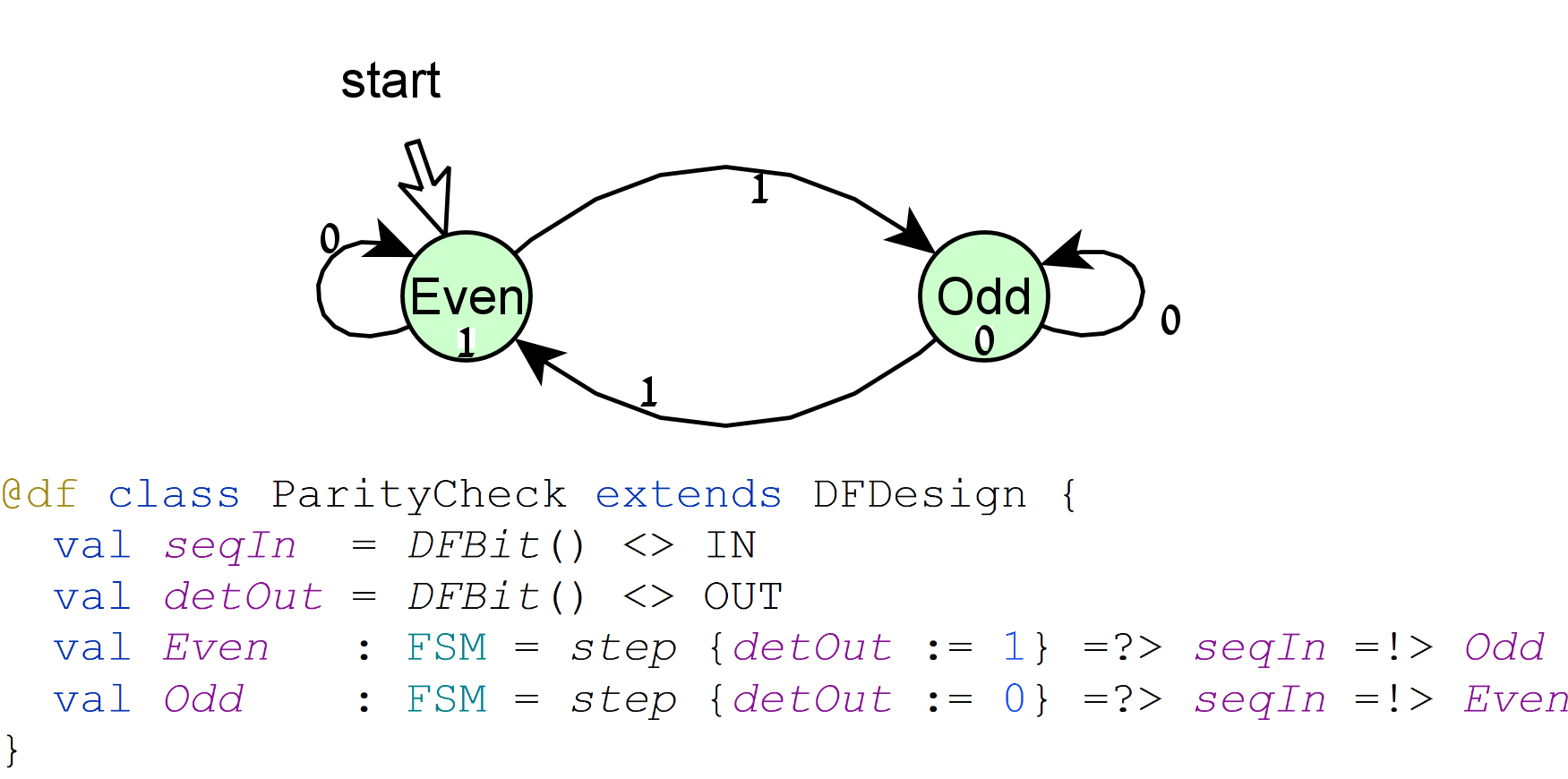

DFiant is a library based on Scala, and as such it embodies strong meta-programming capabilities. Therefore, although DFiant enables the classic FSM description (with a state variable and a case statement), it also provides higher-level constructs to describe the FSM very similarly to the way it is commonly drawn. The following figure includes a diagram of a parity checker and its implementation in DFiant. The parity checker receives a single bit input sequence and outputs a high logic value if the sequence has an even parity.

As you can see, the code is very short and does not need any state variable or case statement. The FSM code constructs two steps, Even and Odd, and connects the step transfer edges according to the `seqIn` input.

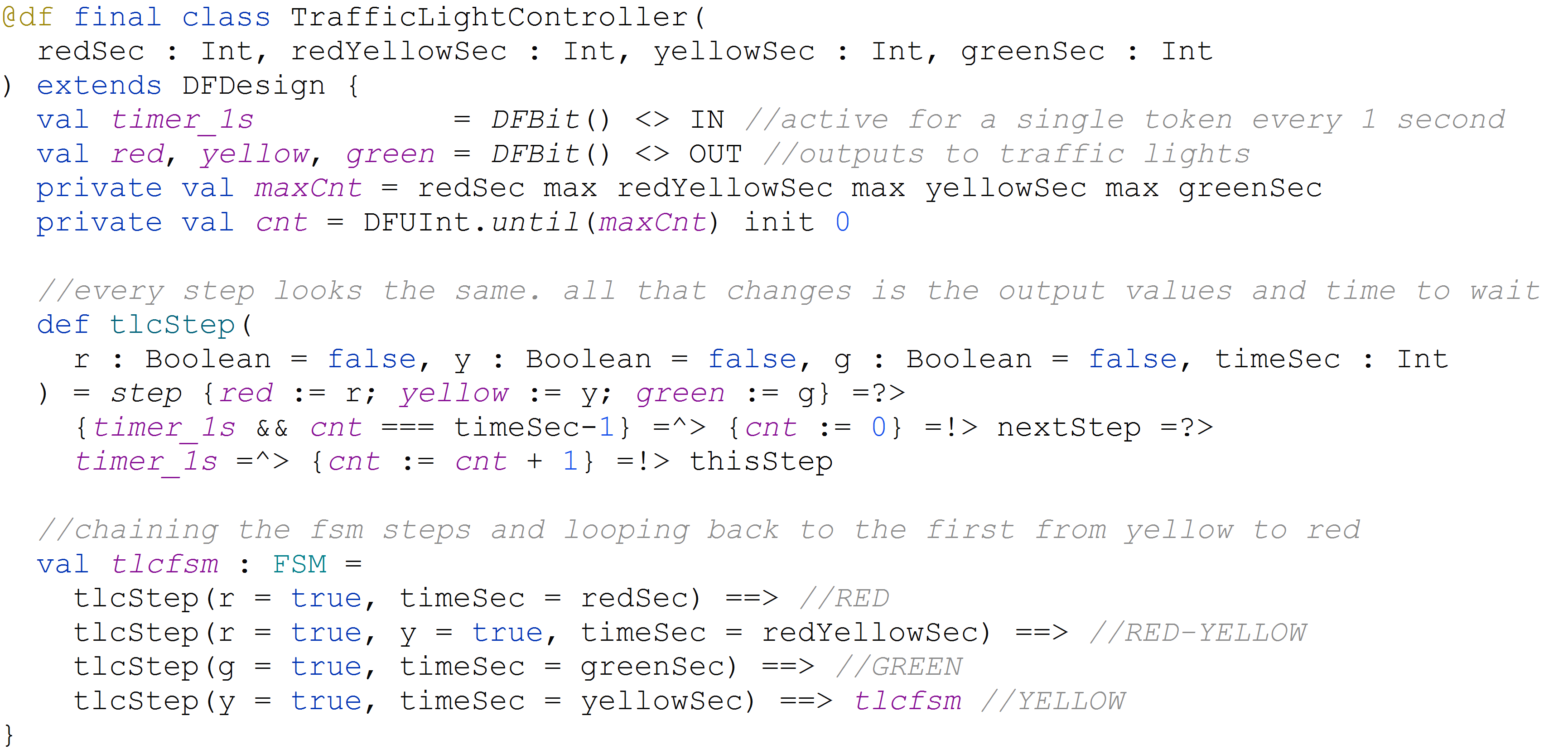

Now for a more complicated example: We want to design a traffic light controller with configurable times for the steps RED, RED-YELLOW, GREEN, YELLOW. The following figure contains a DFiant implementation that uses a single counter that is reset for every step. We will not delve into the code here, but it clearly shows how commonality between the controller steps can be shared and how the steps are chained together to create the full FSM.

Finally, since each step can be chained to another step (or the first step in an FSM), we can provide even higher abstraction constructs that can be chained: doWhile, doUntil, doFor, waitUntil, and others.

In conclusion, DFiant has dataflow HDL semantics, but it also offers sequential-like semantics that are enabled by chaining FSMs together. This capability increases the designer productivity without inhibiting the fine-grain hardware construction control we have come to expect from classic HDLs.

For information of DFiant language, see: https://dfianthdl.github.io/LEGaTO/ and https://github.com/legato-project/DFiant