News & press releases

DFiant: Making hardware design easy

The slowing of Moore’s Law and the ever-increasing need for compute power have breathed new life into the computer processor and accelerator industry. More and more start-up companies developing new processors and accelerators are funded to challenge the perceived stagnation in the processor industry.

Yet a major hurdle that stands in the way of innovation is outdated design languages and methodology. Unlike the software industry, which consistently adopts new languages and concepts, the hardware industry has been highly conservative and still relies on the 30-year-old register-transfer level (RTL) programming model and the dominance of Verilog and VHDL RTL-based hardware description languages (HDLs). While the the software world has moved to a largely “write once, run anywhere“ programmability, the RTL model still mixes design functionality with underlying technology constraints, which inhibits design flexibility across various technologies and core components. Moreover, any change to the timing or device requirements may lead to significant redesigns, since RTL abstractions tightly couple functionality with timing constraints. For example, registers serve various roles such as preserving a state, pipelining and balancing a data path, deriving timed signals from an input clock, and synchronizing an input signal. This coupling between functionality, timing constraints, and device constraints leads to verbose and unportable RTL designs.

The DFiant HDL developed at Technion – Israel Institute of Technology as part of the Horizon 2020 LEGaTO project follows the software path in decoupling design functionality from the underlying technology and promises to greatly improve designer productivity. DFiant proposes dataflow-based HDL abstractions that allow designers to express the design functionality while automatically mapping the design to technology-driven constructs such as registers and clocks. DFiant brings together constructs and semantics from dataflow, hardware, and software programming languages to enable truly portable and composable hardware designs. The dataflow model offers implicit concurrency between independent paths while freeing the designer from explicit register placement that binds the design to fixed pipelined paths and timing constraints.

DFiant offers a path to improve the productivity of hardware designers and challenges ongoing efforts to bridge the hardware programmability gap. By and large, these efforts can be largely split into two classes: high-level synthesis (HLS) tools and high-level RTL (HL-RTL) languages. On the one hand, HLS tools rely on programming languages like C and incorporate auto-pipelining and optimization mechanisms to make hardware accelerators accessible for non-hardware engineers. While this approach is successful in algorithmic acceleration domains, such languages carry von Neumann sequential semantics and thus hinder construction of parallel hardware, which is crucial for hardware design. Moreover, some trivial periodic hardware operations (like toggling a LED) are unbearably difficult to implement in HLS languages. On the other hand, HL-RTL languages (e.g., Chisel, Bluespec, PyRTL) aim to enhance productivity by introducing new hardware generation constructs and semantics but do not abstract away register-level description. Therefore, HL-RTL designs are still subjected to the “tyranny of the clock“ and therefore bound to specific timing and target constraints.

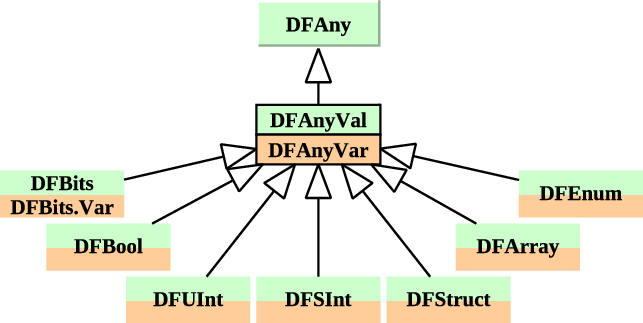

Neither an HLS or RTL, DFiant is an HDL that provides abstractions beyond the RTL behavioral model, which reduce verbosity and maintain portable code. Since DFiant is implemented as a Scala library, it offers a rich type safe ecosystem alongside its own hardware-focused type system (e.g., bit-accurate dataflow types, input/output port types). The library performs two main tasks: First, the frontend compilation, which enforces the type-safe rule system and constructs a dataflow dependency graph; and second, the backend compilation, which translates the graph into pipelined RTL code and a TCL constraints file. The resulting code can be synthesized using commercial tools.

Further reading:

DFiant: A Dataflow Hardware Description Language. Oron Port, Yoav Etsion. 27th International Conference on Field Programmable Logic and Applications (FPL), 2017